# 博士論文

Grain Growth Control by Atmospheric Pressure Micro-Thermal-Plasma-Jet Irradiation on Amorphous Silicon Strips and Its Application to High-Speed CMOS Circuit Fabrication

アモルファスシリコン細線への大気圧

マイクロ熱プラズマジェット照射による

結晶成長制御とその高速 CMOS 回路作製への応用

# 森崎 誠司

広島大学大学院先端物質科学研究科

# 2015年10月

1. 主論文

Grain Growth Control by Atmospheric Pressure Micro-Thermal-Plasma-Jet Irradiation on Amorphous Silicon Strips and Its Application to High-Speed **CMOS Circuit Fabrication**

(アモルファスシリコン細線への大気圧マイクロ熱プラズマジェット 照射による結晶成長制御とその高速 CMOS 回路作製への応用) 森﨑 誠司

- 2. 公表論文

- (1) Improvement in Characteristic Variability of TFTs Using Grain Growth Control by Micro Thermal Plasma Jet Irradiation on a-Si Strips Seiji Morisaki, Shohei Hayashi, Yuji Fujita, and Seiichiro Higashi Journal of Display Technology 10, 950-955 (2014).

- (2) Effect of Grain Growth Control by Atmospheric Micro-Thermal- Plasma-Jet Crystallization of Amorphous Silicon Strips on TFT Characteristics Seiji Morisaki, Shohei Hayashi, Shogo Yamamoto, Taichi Nakatani, and Seiichiro Higashi

ECS Transaction 64, 23-29 (2014).

- 3. 参考論文

- (1) Investigation of Silicon Grain Structure and Electrical Characteristics of TFTs Fabricated Using Different Crystallized Silicon Films by Atmospheric Pressure Micro-Thermal-Plasma-Jet Irradiation Shohei Hayashi, Seiji Morisaki, Takahiro Kamikura, Shogo Yamamoto, Kohei Sakaike, Muneki Akazawa, and Seiichiro Higashi Japanese Journal of Applied Physics 53, 03DG02 (2014)

- (2) Investigations on crack generation mechanism and crack reduction by buffer layer insertion in thermal-plasma-jet crystallization of amorphous silicon films on glass substrate

Keisuke Tanaka, Shohei Hayashi, Seiji Morisaki, and Seiichiro Higashi Japanese Journal of Applied Physics 54, 01AE05 (2015).

主論文

# Abstract

From the beginning of 2000s, flat panel displays (FPDs), such as liquid crystal displays (LCDs) and organic light emitting displays (OLEDs), have been widely in practical use for television (TVs), personal computers (PC), and mobile device. In order to drive the pixel of FPDs, an active-matrix driving method has been adopted by taking over the Cathode ray tube (CRT) in the past. FPDs, which are based on large area electronics, have been achieved remarkable development to enlarge and dilute the size of displays. It should be noted that thin film transistors (TFTs) had contributed to the remarkable development of FPDs. Hydrogenated amorphous silicon (a-Si:H) film was used for fabrication of TFTs as a switching device for pixels. Resent years, however, small and middle-sized displays, such as smart phone, tablet and wearable displays, have rapidly come into wide use. For these portable displays, high-reliability and higher-resolution than 500 pixels per inch (ppi), which is far beyond the limit resolution of human eyes, were strictly required. In addition, with the object of battery operation, low-power consumption is strictly required. With the shrink of pixel size and the increase of pixel number, the formation of narrow flames was strictly required because the number of wiring around display area rapidly increased.

In terms of field effect mobility ( $\mu_{FE}$ ) higher than 100 cm<sup>2</sup>/Vs, high-reliability and the exclusive capability of complementary metal-oxide semiconductor (CMOS) fabrication, crystalline silicon (c-Si) technology is quite promising for next generation displays with low power consumption and multi-functions. Excimer laser annealing (ELA) has been widely utilized for fabrication of c-Si TFTs. However, because of the expensive equipment and running cost, lower fabrication cost technique has been required. In addition, c-Si TFTs has a critical issue of variation. TFT characteristics were sensitive to defects, such as grain boundaries (GBs) and intra-grain defects. The key research purposes for higher performance TFT is to enlarge the grain size. However, with increase of grain size, the characteristic variability of TFTs has become critical issue instead of high- $\mu_{FE}$ . Especially, the variation of threshold voltage prevents the operation at a low supplying voltage, namely, low power consumption.

For these issues, we have proposed new crystallization technique of thermal plasma jet (TPJ) and advanced micro-TPJ ( $\mu$ -TPJ) with higher plasma density. Because of its simple structure and atmospheric pressure process,  $\mu$ -TPJ enables low fabrication of TFT. In our previous work, grains larger than ~60  $\mu$ m were formed by high-speed lateral crystallization (HSLC) using micro-thermal-plasma-jet ( $\mu$ -TPJ) irradiation. In addition, we have

demonstrated a high field effect mobility of 350  $\text{cm}^2/\text{Vs}$  with HSLC by a high scanning speed (*v*) of 4000 mm/s. However, random grain boundaries (GBs) were formed by HSLC. Random GBs cause characteristic variability in thin film transistors (TFTs).

In this work, we attempted to control the grain growth using  $\mu$ -TPJ irradiation on a-Si patterns. This approach is promising for high performance TFT with low fabrication cost because additional and difficult process step are not necessary by applying the grain growth controlling pattern to active layer of TFT. We attempted to improve the variation issue and to operate CMOS circuit by a low voltage at a high speed. I will discuss about the practicability based on research results in this thesis.

In chapter 1, the back grounds of c-Si TFTs for fabrication of FPDs were described. The crystallization of a-Si and CMOS formation on glass substrate is required for industry.

In chapter 2, I will describe about the developments of TPJ andµ-TPJ crystallization technique. TPJ formed small grains with ~100 nm and its application to TFT fabrication was demonstrated. NMOS and PMOS TFTs was successfully operated with  $\mu_{FE}$  of ~20 cm<sup>2</sup>/Vs. While this result was promising for CMOS fabrication, the improvement of TFT performance was required. So µ-TPJ was developed to form larger size of grains. Grains with ~60 µm were formed by high-speed lateral crystallization (HSLC) after liquid phase crystallization. By applying HSCL to TFT fabrication, TFT with high  $\mu_{FE}$  of 350 cm<sup>2</sup>/Vs was achieved.

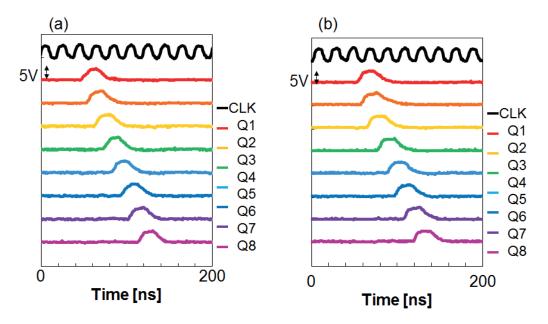

In chapters from 3 to 6, the research results are described. In chapter 3, we improved the most important issue of variation in TFTs. we have proposed a new TFT pattern which is composed of 1- $\mu$ m-wide strip channels. This strip channel is effective to suppress random GBs by filtering effects. In addition, by applying this strip to channel area of TFTs, field effect mobility higher than 300 cm<sup>2</sup>/Vs with significantly low variation were achieved. This high-performance enabled us to operate CMOS circuits. We were able to operate 8-bit shift-register at a supply voltage of 5V and a clock frequency of 4 MHz.

In chapter 4, the relationship between channel crystallinity and TFT characteristics were investigated. After eliminating random GBs, a small amount less than  $1.0 \times 10^{17}$  cm<sup>-3</sup> of intra-grain defects were formed in channel area. In order to miniaturize TFTs, accurate control of Fermi-level is important.

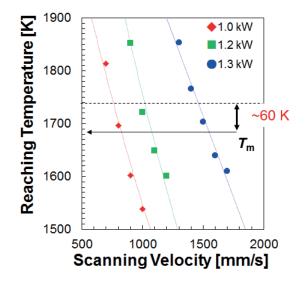

In chapter 5, the mechanism of defect formation was investigated. The agglomeration of liquid Si affected to the formation of intra-grain defects. In order to suppress these defects,  $\mu$ -TPJ condition was optimized. By controlling the reaching temperature of liquid Si less at most 1747 K, intra-grain was extremely suppressed.

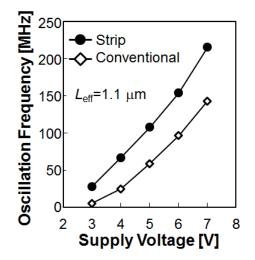

In chapter 6, we attempted to operate short channel TFT and CMOS circuit at a very high speed. Using optimized  $\mu$ -TPJ condition and strip pattern, TFTs with high  $\mu_{FE}$  of 500 cm<sup>2</sup>/Vs were achieved. A 9-stage ring oscillator fabricated with strip channel TFTs,

oscillation frequency increased to 108 MHz and the delay time decreased to 0.52 ns at a supply voltage of 5V. The cut-off frequency of 1.9 GHz was achieved by  $\mu$ -TPJ crystallization technique.

From the achievement of this research, we could demonstrate the practicability of  $\mu$ -TPJ crystallization technique for next generation displays in terms of the high-performance TFTs and its low process cost.

# Contents

# Chapter 1 :

| Introduction                                    | 1 |

|-------------------------------------------------|---|

| 1.1 Background                                  |   |

| 1.1.1 Flat panel display                        | 2 |

| 1.1.2 Thin-film transistor                      | 2 |

| 1.1.3 Fabrication of crystalline-silicon film   | 3 |

| 1.1.4 CMOS circuit formation on glass substrate | 4 |

| 1.2 Overview of thesis                          |   |

| 1.2.1 Motivation and purpose                    | 5 |

| 1.2.2 Components                                | 5 |

| References                                      | 7 |

### Chapter 2 :

| Fabrication of Thin Film Transistor by Micro-Thermal-Plasma-Jet                |    |

|--------------------------------------------------------------------------------|----|

| Crystallization                                                                | 11 |

| 2.1 Application of TPJ irradiation to TFT fabrication                          | 12 |

| 2.2 Noncontact temperature measurement of TPJ irradiation                      | 17 |

| 2.3 Fabrication of NMOS and PMOS TFTs                                          | 20 |

| 2.4 High-speed lateral crystallization by micro-thermal plasma jet irradiation | 23 |

| References                                                                     | 29 |

# Chapter 3 :

| Improvement of Characteristic Variability in TFTs by Micro Thermal                  |      |

|-------------------------------------------------------------------------------------|------|

| Plasma Jet irradiation on Amorphous Silicon Strips                                  | 31   |

| 3.1 Introduction                                                                    | 32   |

| 3.2 Experimental procedure                                                          |      |

| 3.2.1 Grain growth control using a-Si strip patterns                                | 33   |

| 3.2.2 In-situ observation of grain growth in a-Si patterns during µ-TPJ irradiation | . 34 |

| 3.2.3 Fabrication of CMOS-TFTs with strip channel                                   | 35   |

| 3.2.4 Operation of CMOS circuits with strip pattern TFTs                            | 36   |

| 3.3 Results and discussion                                                          |      |

| 3.3.1 Grain growth induced by µ-TPJ irradiation on a-Si pattern                     | 37   |

| 3.3.2 In-situ observation of grain growth in a-Si patterns during $\mu$ -TPJ irradiation | 42   |

|------------------------------------------------------------------------------------------|------|

| 3.3.3 Self-aligned top gate CMOS TFT fabrication                                         | . 47 |

| 3.3.4 CMOS circuit operation                                                             | . 49 |

| 3.4 Summary                                                                              | . 52 |

| References                                                                               | . 53 |

### Chapter 4 :

| Investigation of the Effects and Crystallinity of Strip Patterns              | 55            |

|-------------------------------------------------------------------------------|---------------|

| 4.1 Introduction                                                              | 56            |

| 4.2 Experimental procedure                                                    | 57            |

| 4.2.1 Investigation of the correlation between TFT characteristics and its of | crystallinity |

|                                                                               | 57            |

| 4.3 Results and discussion                                                    |               |

| 4.3.1 Investigation of the correlation between TFT characteristics and its of | crystallinity |

|                                                                               | 59            |

| 4.4 Summary                                                                   | 67            |

| References                                                                    | 68            |

## Chapter 5 :

| Investigation of Intra-Grain Defect Formation in Amorphous Silicon               |    |

|----------------------------------------------------------------------------------|----|

| Strips During Micro-Thermal-Plasma-Jet Irradiation                               | 69 |

| 5.1 Introduction                                                                 | 70 |

| 5.2 Experimental procedure                                                       |    |

| 5.2.1 Improvement of GBs and intra-grain defects in a-Si strips                  | 71 |

| 5.2.2 Optimization of the condition by μ-TPJ crystallization on a-Si strips      | 71 |

| 5.3 Results and discussion                                                       |    |

| 5.3.1 Improvement of GBs and intra-grain defects in a-Si strips                  | 73 |

| 5.3.2 Optimization of the condition by $\mu$ -TPJ crystallization on a-Si strips | 77 |

| 5.4 Summary                                                                      | 79 |

| Reference                                                                        | 80 |

## Chapter 6 :

| High-Speed Operation of CMOS Circuit with Short Channel TFTs                           | 81 |

|----------------------------------------------------------------------------------------|----|

| 6.1 Introduction                                                                       | 82 |

| 6.2 Experimental procedure                                                             |    |

| 6.2.1 Characteristic variability of short channel TFTs with respect to channel width . |    |

|                                                                                        | 83 |

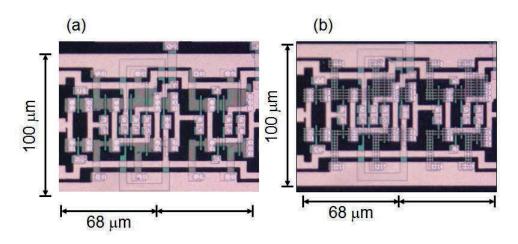

| 6.2.2 CMOS circuit operation using short channel TFTs                                  | 84 |

| 6.3 Results and discussion                                                            |    |

|---------------------------------------------------------------------------------------|----|

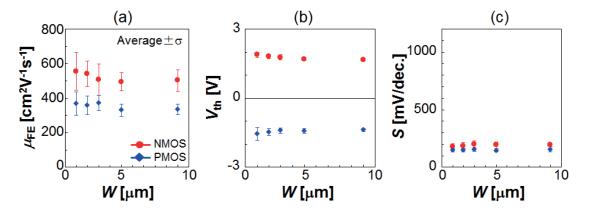

| 6.3.1 Characteristic variability of short channel TFTs with respect to channel width. |    |

|                                                                                       | 85 |

| 6.3.2 CMOS circuit operation using short channel TFTs                                 | 89 |

| 6.4 Summary                                                                           | 92 |

| References                                                                            | 93 |

| Conclusion                                                                            | 95 |

| Acknowledgement                                                                       | 97 |

| List of Publications and Awards                                                       | 99 |

# Chapter 1

# Introduction

#### 1.1 Background

#### 1.1.1 Flat panel display

From the beginning of 2000s, flat panel displays (FPDs), such as liquid crystal displays (LCDs) and organic light emitting displays (OLEDs), have been widely in practical use for television (TVs), personal computers (PC), and mobile device. In order to drive the pixel of FPDs, an active-matrix driving method has been adopted by taking over the Cathode ray tube (CRT) in the past. FPDs, which are based on the large area electronics, have been achieved development to enlarge or dilute the size of displays. It should be noted that thin film transistors (TFTs) had contributed the remarkable development of FPDs. Hydrogenated amorphous silicon (a-Si:H) film was used for fabrication of TFTs as a switching device for pixels of a display [1-2]. By enlargement of mother glass size, a-Si:H TFTs have achieved low fabrication cost. At this moment, the  $10^{th}$  generation glass substrate with the width of 3 m × 3 m has used for the large sized displays. It can be said that the mother glass size is limited by the width of roadway.

In resent year, however, small and middle-sized displays, such as smart phone, tablet and wearable displays, have rapidly come into wide use because of their portability. For these portable displays, high-reliability and higher-resolution than 500 pixels per inch (ppi), which is far beyond the limit resolution of human eyes, were strictly required [3]. In addition, with the object of battery operation, low-power consumption is strictly required. Instead of LCDs, organic electro-luminescence diode (OLED) displays have been developed. Because of a self-luminous device, OLED is quite promising for lower power consumption compared to LCD, which consumes away approximately 70% of a backlight.

For driving the pixels of both of LCDs and OLED displays, development of TFT is one of the most important technological issue for next generation displays.

#### 1.1.2 Thin-film transistor

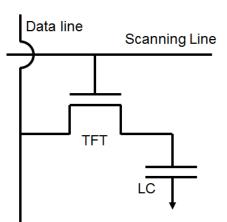

For the AM-LCDs, TFTs are connected with data lines and scanning lines as shown in Fig. 1.1. In order to drive each pixels, TFTs are required high- on/off ratio ( $R_{on/off}$ ) of current. In the case of large sized displays, a-Si:H film is applied because of its uniform deposition, in spite of a low field effect mobility ( $\mu_{FE}$ ) of ~ 0.5 cm<sup>2</sup>/Vs [1-2]. In the case of small sized displays, however, in order to achieve higher resolution, small sized TFTs are required. So in order to contain high  $R_{on/off}$ , alternative channel materials with higher  $\mu_{FE}$  have been developed. by increase of pixel numbers and frame rate. For new channel materials, an organic TFT [4-6], oxide TFT [7-12], and crystalline Si (c-Si) TFT including

Fig. 1.1. Circuit diagram of TFT for driving pixel of LCD.

polycrystalline silicon (poly-Si) [13-43] have been studied. Above all, oxide and c-Si TFTs come into practical use.

In terms of  $\mu_{FE}$  higher than 100 cm<sup>2</sup>/Vs, high-reliability and the exclusive capability of complementary metal-oxide semiconductor (CMOS) fabrication, c-Si technology is quite promising for next generation displays with low power consumption and multi-functions.

#### 1.1.3 Fabrication of crystalline-silicon film

The c-Si films are formed by direct deposition techniques such as low pressure chemical vapor deposition (LPCVD) [13-16], plasma enhanced CVD (PECVD) [17], sputtering [18] and reactive thermal CVD [19]. However, in order to form c-Si on a substrate, generally temperature higher than 600°C is necessary. Because this temperature is higher than heat-resistance of glass substrate, low temperature fabrication process using rapid thermal annealing of a-Si film has developed. Excimer laser annealing (ELA) has been widely utilized. By investigation of the mechanism about crystallization by ELA, large grains with the size of several hundred nm are formed by melting and crystallizing Si films within nanosecond period [20-25]. However, because of the expensive equipment and running cost, various crystallization techniques utilizing pulsed-laser crystallization [20-25], solid-phase crystallization (SPC) [26], metal-induced crystallization [27-28], continuous-wave (CW) laser crystallization [29 - 33], flash lamp annealing (FLA) [34-35], and thermal plasma jet (TPJ)[36-40] have been studied industriously. The key research purposes for higher performance TFT is to enlarge the grain size using these crystallization techniques, including ELA [41-44]. Conventionally, large grains are formed after phase transformation of liquid phase by zone-melting recrystallization (ZMR).

However, with increase of grain size, the characteristic variability of TFTs has become critical issue instead of high- $\mu_{FE}$ . These variation and degradation of TFTs are caused by

crystal defects in channel region, such as grain boundaries (GBs) and intra-grain defects[45 - 47]. So advanced crystallization technique with the aim of the location control of GBs and termination method of defects have been developed.[48-51]

#### 1.1.4 CMOS circuit formation on glass substrate

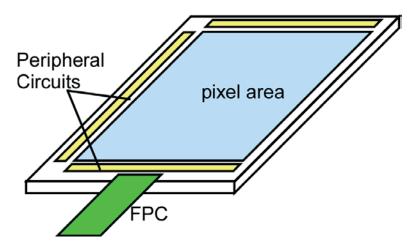

As mentioned in Sect. 1.1.2, c-Si TFT has a capability of CMOS fabrication and a high- $\mu_{FE}$ . The  $\mu_{FE}$  higher than 100 cm<sup>2</sup>/Vs is promising for circuit operation at a high speed, and CMOS structure is quite effective for low power consumption. These advantage enables a circuit formation on glass substrate as same as pixel area, what is called system on panel (SOP) [52-54]. By increasing the number and resolution of pixels, the number of wirings increases. In order to drive each pixels, a control circuit must be connected to wirings with a large number and narrow pitch dependent of pixels. This incurs higher fabrication cost because of the difficulty of packaging or enlargement of frame. For the small sized displays, narrow frame is strictly required in order shrink the total size.

To solve this issue, SOP technique has developed as shown in Fig. 1.2. By the formation of peripheral circuit on glass substrate, the number of wirings is extremely suppressed and narrow frame is achieved [53-54]. In addition, for the lower power consumption by low supply voltage and higher speed operation, improvement of TFT performance, such as low threshold voltage ( $V_{\text{th}}$ ) and  $\mu_{\text{FE}}$  higher than 300 cm<sup>2</sup>/Vs, is required.

Fig. 1.2. Schematic diagram of system on panel (SOP) on glass substrate.

#### **1.2** Overview of thesis

#### 1.2.1 Motivation and purpose

In our previous works, we proposed the application of an atmospheric-pressure direct current (DC) arc discharge thermal-plasma-jet (TPJ) to the crystallization of a-Si films on quartz substrates. This innovative technique has been demonstrated its capability for the application to industry by its TFT performance. In addition, advanced plasma induced crystallization method of micro-thermal plasma jet ( $\mu$ -TPJ), which generates higher density of plasma, has been proposed [55 - 56]. Large grains with ~60 µm were formed by  $\mu$ -TPJ irradiation and demonstrated a high-performance TFT with a field effect mobility ( $\mu_{FE}$ ) of 350 cm<sup>2</sup>/Vs. These high crystallinity and high-performance TFT were quite promising for the application to industry because of its cost fabrication cost. However, by increasing the grain size and TFT performance, significant issue of variability in TFTs were also stood out as same as other LTPS technique. So in this work, we forced on this variation issue, which is the most important to be practical use of  $\mu$ -TPJ.

#### 1.2.2 Components

This doctoral thesis was composed of following chapters.

Chapter 1: Introduction Chapter 2: Fabrication of Thin Film Transistor by Micro-Thermal-Plasma-Jet Crystallization Chapter 3: Improvement of Characteristic Variability in TFTs by Micro-Thermal-Plasma-Jet irradiation on Amorphous Silicon Strips Chapter 4: Investigation of the Effects and Crystallinity of Strip Patterns Chapter 5: Investigation of Intra-Grain Defect Formation in Amorphous Silicon Strips During Micro-Thermal-Plasma-Jet Irradiation Chapter 6: High-Speed Operation of CMOS Circuit with Short Channel TFTs

In previous work, TPJ and  $\mu$ -TPJ applied for the crystallization of a-Si films. These techniques for crystallization and application of TFT fabrication are introduced in Chap. 2. Experimental results and discussions were described in Chap. 3 ~ 6. In Chap. 3, the variation issue was significantly improved by the control of grain growth using  $\mu$ -TPJ irradiation on a-Si strips. A new TFT pattern was proposed and demonstrated high-performance TFTs with low variation by suppressing random GBs. CMOS circuits were successfully operated at a low supplying voltage. We attempted to operate CMOS circuit at a higher speed. Our approaches are as follows. In Chap. 4, we investigated the

relationship between TFT performance and the channel crystallinity. A small amount of defects were still formed in crystallized channels while GBs were eliminated out. It was extremely important to control the Fermi level as same as single-crystalline silicon because of its high crystallinity. In addition, higher crystallinity channel was required for short channel TFTs. So we focused on intra-grains in crystallized Si. In Chap. 5, the mechanism of intra-defects formation was investigated and improved crystallization method of  $\mu$ -TPJ. The control of properties of liquid Si is important to suppress the intra-grain defects. In Chap. 6, we attempted CMOS circuit at a very high speed based on the results in Chap. 3 to 5. It should be noted that the most important approach for high performance TFT was based on crystallization.

#### References

- [1] C. -S. Yang, L. L. Smith, C. B. Arthur, and G. N. Parsons, J. Vac. Sci. Technol. B 18, 683 (2000).

- [2] A. Sazonov and A. Nathan, J. Vac. Sci. Technol. A 18, 780 (2000).

- [3] T. Iizuka, Y. Hisatake, H. Kimura, T. Nishibe, and Y. Takubo: Proc. AM-FPD '13, 2013, p. 219.

- [4] M. Uno, Y. Tominari, and J. Takeya, Appl. Phys. Lett. 93, 173301 (2008).

- [5] M. Uno, I. Doi, K. Takimiya, and J. Takeya, Appl. Phys. Lett. 94, 103307 (2009).

- [6] H. Minemawari, T. Yamada, H. Matsui, J. Tsutsumi, S. Haas, R. Chiba, R. Kumai, and T. Hasegawa, Nature 475, 364 (2011).

- [7] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature 432, 488 (2004).

- [8] H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, Appl. Phys. Lett. 89, 112123 (2006).

- [9] T. Osada, K. Akimoto, T. Sato, M. Ikeda, M. Tsubuku, J. Sakata, J. Koyama, T. Serikawa, and S. Yamazaki, Jpn. J. Appl. Phys. 49, 03CC02 (2010).

- [10] K. Toyotaka, K. Kusunoki, T. Nagata, Y. Hirakata, K. Wakimoto, J. Koyama, S. Yamazaki, R. Sato, K. Okazaki, and M. Sakakura, Jpn. J. Appl. Phys. 50,03CC09 (2011).

- [11] Y. Nonaka, Y. Kurosawa, Y. Komatsu, N. Ishihara, M. Oota, M. Nakashima, T. Hirohashi, M. Takahashi, S. Yamazaki, T. Obonai, Y. Hosaka, J. Koezuka, and J. Yamauchi, J. Appl. Phys. 115, 163707 (2014).

- [12] S. Yamazaki, ECS Trans. 64 [10], 115 (2014).

- [13] S. Onga, Y. Mizutani, K. Taniguchi, M. Kashiwagi, K. Shibata, and S. Kohyama, Jpn. J. Appl. Phys. 21, 1472 (1982).

- [14] D. B. Meakin, N. A. Economou, P. A. Coxon, J. Stoemenos, A. Lowe, and P. Migliorato, Appl. Surf. Sci., 30, 372 (1987).

- [15] T. W. Little, K. Takahara, H. Koike, T. Nakazawa, I. Yudasaka, and H. Ohshima, Jpn. J. Appl. Phys. 30, 3724 (1991).

- [16] M. Miyasaka, T. Nakazawa, I. Yudasaka, and H. Ohshima, Jpn. J. Appl. Phys. 30, 3733 (1991).

- [17] J. I. Woo, H. J. Lim, and J. Jang, Appl. Phys. Lett. 65, 1644 (1994).

- [18] Y. Mishima, M. Takei, T. Uematsu, N. Matsumoto, T. Kakehi, U. Wakino, and M. Okabe, J. Appl. Phys. 78, 217 (1995).

- [19] J. W. Lee, K. Shimizu, and J. Hanna, J. Non-Cryst. Solids 38, 173 (2004).

- [20] K. Sera, F. Okumura, H. Uchida, S. Itoh, S. Kaneko, and K. Hotta, IEEE Trans.

Electron Devices 36, 2868 (1989).

- [21] T. Sameshima, M. Hara, and S. Usui, Jpn. J. Appl. Phys. 28, 1789 (1989).

- [22] J. S. Im, H. J. Kim, and M. O. Thompson, Appl. Phys. Lett. 63, 1969 (1993).

- [23] M. Hatano, S. Moon, M. Lee, K. Suzuki, and C. P. Grigoropoulos, J. Appl. Phys. 87, 36 (2000).

- [24] S. Higashi and T. Sameshima, Jpn. J. Appl. Phys. 40, 480 (2001).

- [25] R. Ishihara, M. He, V. Rana, Y. Hiroshima, S. Inoue, T. Shimoda, J. W. Metselaar, and C. I. M. Beenakker, Thin Solid Films 487, 97 (2005).

- [26] T. Noguchi, Jpn. J. Appl. Phys. 32, L1584 (1993).

- [27] K. Makihira and T. Asano, Appl. Phys. Lett. 76, 3774 (2000).

- [28] M. Kurosawa, N. Kawabata, T. Sadoh, and M. Miyao, Appl. Phys. Lett. 95, 132103 (2009).

- [29] A. Hara, F. Takeuchi, M. Takei, K. Suga, K. Yoshino, M. Chida, Y. Sano, and N. Sasaki, Jpn. J. Appl. Phys. 41, L311 (2004).

- [30] S. -I. Kuroki, Y. Kawasaki, S. Fujii, K. Kotani, and T. Ito, J. Electrochem. Soc. **158**, H924 (2011).

- [31] C. Chou, I. Lee, P. Yang, M. Hu, C. Wang, C. Wu, Y. Chien, K. Wang, and H. Cheng, Appl. Phys. Lett. 103, 053515 (2013).

- [32] J. S.Im, M. Chahal, P. C. Wilt, U. J. Chung, G. S. Ganot, A. M. Chitu, N. Kobayashi, K.Ohmori, A.B.Limanov, J. Cryst Growth 312, 2775 (2010).

- [33] T. Okada, J. de Dieu Mugiraneza, K. Shirai, T. Suzuki, T. Noguchi, H. Matsushima, T. Hashimoto, Y. Ogino, and E. Sahota, Jpn. J. Appl. Phys. 51, 03CA02 (2012).

- [34] M. Smith, R. McMahon, M. Voelskow, D. Panknin, and W. Skorupa, J. Cryst. Growth 285, 249 (2005).

- [35] K. Ohdaira, Y. Endo, T. Fujiwara, S. Nishizaki, and H. Matsumura, Jpn. J. Appl. Phys. 46, 7603 (2007).

- [36] H. Kaku, S. Higashi, H. Taniguchi, H. Murakami, and S. Miyazaki, Appl. Surf. Sci. 244, 8 (2005).

- [37] S. Higashi, H. Kaku, H. Taniguchi, H. Murakami, and S. Miyazaki, Thin Solid Films 487, 122 (2005).

- [38] S. Higashi, H. Kaku, H. Murakami, S. Miyazaki, and H. Wakatabe, Jpn. J. Appl. Phys. 44, L108 (2005).

- [39] T. Yorimoto, S. Higashi, H. Kaku, T. Okada, H. Murakami, S. Miyazaki, T. Matsui, A. Masuda, and M. Kondo, Jpn. J. Appl. Phys. 47, 6949 (2008).

- [40] S. Higashi, K. Sugakawa, H. Kaku, T. Okada, and S. Miyazaki, Jpn. J. Appl. Phys. 49, 03CA08 (2010).

- [41] H. J. Kim and James S. Im, Appl. Phys. Lett. 68, 1513 (1996).

- [42] A. Limanov, V. Borisov, : Proc. Mat. Res. Soc. Symp, 2013, p. D10.1.1.

- [43] R. Vikas, R. Ishihara, Y. Hiroshima, D. Abe, S. Inoue, T. Shimoda, W. Metselaar, and K. Beenakker, Jpn. J. Appl. Phys. 45, 4340 (2006).

- [44] Y. Takamia, T. Warabisakob, M. Matsumura, ECS Trans., 3 [8] 127 (2006).

- [45] M. Kimura, S. Inoue, T. Shimoda, and T. Sameshima, Jpn. J. Appl. Phys. 40, L97 (2001).

- [46] M. Kimura, Jpn. J. Appl. Phys. 50, 03CB01 (2011).

- [47] M. Kimura and A. Nakashima, Jpn. J. Appl. Phys. 51, 03CA05 (2012).

- [48] H. Watakabe, T. Sameshima, Appl. Phys. A77, 141 (2003).

- [49] H. Watakabe and T. Sameshima, IEEE Trans. Electron device 49, 2217 (2002).

- [50] Y. Tsunoda, T. Sameshima and S. Higashi, Jpn. J. Appl. Phys. 39, 1656 (2000).

- [51] S. Higashi, D. Abe, Y. Hiroshima, K. Miyashita, T. Kawamura, and S. Inoue: IEEE Electron Device Lett. **23** [7], 407 (2002).

- [52] J. Ohwada, M. Takabatake, Y. A. Ono, A. Mimura, K. Ono, and N. Konishi, IEEE Trans. Electron Devices 36, 1923 (1989).

- [53] M. Takabatake, J. Ohwada, Y. A. Ono, K. Ono, A. Mimura, and N. Konishi, IEEE Trans. Electron Devices 38, 1303 (1991).

- [54] K. M. Lim, K. Lee, M. K. Baek, B. Y. Lee, J. Yoon, E. Kim, J. Yu, Y. Park, Y. S. Yoo, Y. Kim, H. Kang, C. Kim, and I. Chung, Displays 27, 191 (2006).

- [55] S. Hayashi, S. Higashi, H. Murakami, and S. Miyazaki: Appl. Phys. Express 3, 061401 (2010).

- [56] S. Higashi, S. Hayashi, Y. Hiroshige, Y. Nishida, H. Murakami, and S.Miyazaki, Jpn. J. Appl. Phys. **50**, 03CB10 (2011).

# Chapter 2

# Fabrication of Thin Film Transistor by Micro-Thermal-Plasma-Jet Crystallization

### 2.1 Application of TPJ irradiation to TFT fabrication

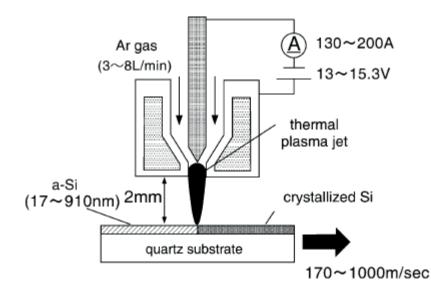

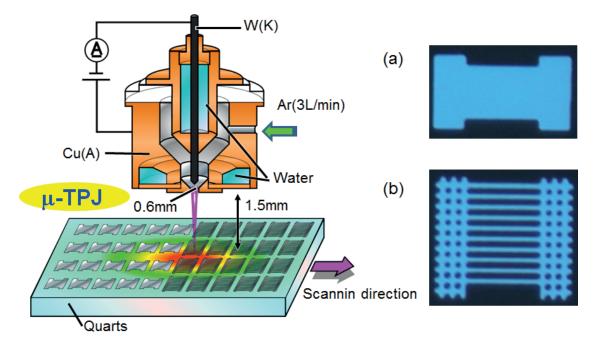

An excimer laser annealing (ELA) has been utilized as a crystallization technique of amorphous Si (a-Si) film as mentioned in Sect. 1.1.3. However, a lower cost crystallization technique is required for the large area electronics because of the high fabrication cost by ELA. We proposed the application of an atmospheric-pressure direct current (DC) arc discharge thermal plasma jet (TPJ) to the millisecond crystallization of a-Si films on quartz substrates [1-5]. Schematic diagram of TPJ crystallization is shown in Fig. 2.1. An anode and a cathode electrodes were made from copper (Cu) and tungsten (W), respectively. Arc discharge was generated by supplying DC power (P) between an anode and a cathode electrodes. TPJ was generated by blowing out the thermal plasma using Argon (Ar) gas thorough the orifice ( $\Phi$ ) of 4 mm in a diameter. Ar gas flow rate and the distance between substrate and TPJ are shown by f and d, respectively. The substrate was lineally moved by a motion stage with a scanning speed (v) in front of TPJ.

Fig. 2.1. Schematic diagram of crystallization of a-Si films on quartz substrate by TPJ irradiation. The TPJ is formed by blowing out the Ar arc plasma through a 4 mm  $\Phi$  nozzle [5].

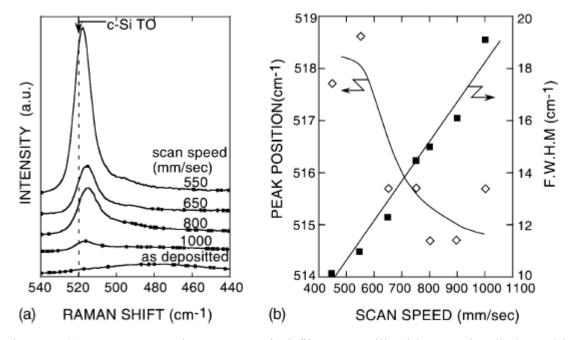

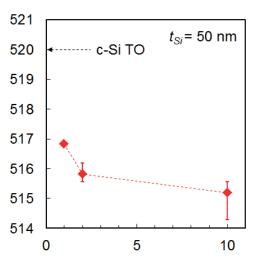

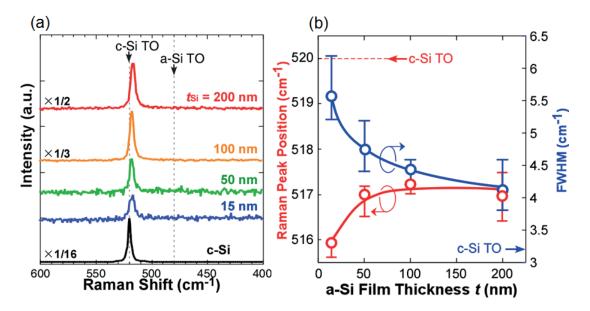

Figure 2.2 shows the Raman scattering spectra of crystallized Si film by TPJ irradiation with different *v*. As shown in Fig. 2.2 (a), the c-Si transversal optical (TO) phonon peak appears after TPJ crystallization. By decreasing *v*, the full width at half maximum (FWHM) gradually decreased and the peak positions were close to the single c-Si at 520 cm<sup>-1</sup> (Fig. 2.2 (b)). From these results, the crystallinity of Si film was improved by TPJ crystallization with slow *v* because of the higher temperature conditions by long annealing duration.

Fig. 2.2. (a) Raman scattering spectra of Si films crystallized by TPJ irradiation with different v. (b) FWHM and position of the c-Si TO phonon peaks. The Si film thickness is 80 nm, and P is ~2.4 kW [5].

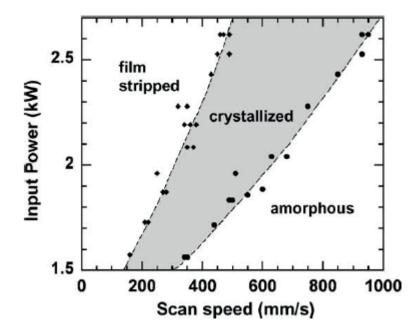

Fig. 2.3. Phase diagram of the Si film after the crystallization as functions of P and v. With increase of P, a-Si films are crystallized at higher v and the process window becomes larger. However, the film stripping was facilitated with decreasing v. [2]

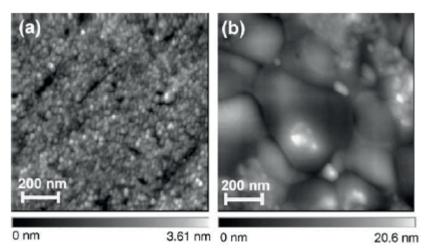

Fig. 2.4. AFM images of 20-nm-thick Si films crystallized in (a) SPC and (b) LPC modes. Typical grain sizes of (a) and (b) were 20 to 30 nm and 300 to 600 nm,respectively.[2]

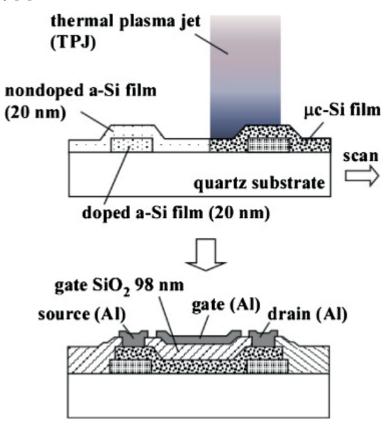

Fig. 2.5. Schematic diagram of TFT fabrication process using TPJ crystallization.[5]

As shown in Fig. 2.3, by increasing P, a-Si films are crystallized at higher v and the process window becomes larger. However, the film stripping was facilitated with a

decrease in the v down to a certain value. The surface morphology by atomic force microscopy (AFM) of the Si film crystallized in solid phase crystallization (SPC) show fine grain structure with the typical size from 20 to 30 nm, while that of the film crystallized in liquid phase crystallization (LPC) mode show much larger grain structure with typical size around 300 to 600 nm, as shown in Figs. 2.4 (a) and (b). The surface roughness increased from 0.5 to 3.4 nm in RMS value. These results suggest that large grains are formed by LPC conditions. In this experiment, however, the process window of LPC was extremely narrow and silicon films ware easily stripping with LPC condition because dehydrogenation was not carried out before crystallization. Moreover, the grain size was still under submicron.

In addition, thin-film transistors (TFTs) with a top-gate structure were formed using SPC film by TPJ crystallization. The process steps were as follows (Fig. 2.5) [5]. Phosphorus-doped a-Si films with a thickness ( $t_{Si}$ ) of 20 nm were deposited by plasma-enhanced chemical vapor deposition (PECVD) on quartz substrate. After formation of source (S) and drain (D) regions by chemical dry etching (CDE), non-doped a-Si films with  $t_{Si} = 20$  nm were deposited by PECVD at 250°C. TPJ was irradiated for crystallization and dopant activation simultaneously. TPJ crystallization was performed with P = 2.3 kW, d = 2 mm, and v = 350 - 550 mm/s. After etching the Si layer to form S, D, and channel (C) by CDE, a 98-nm-thick gate SiO<sub>2</sub> was deposited at 300°C by remote-PECVD. After formation of contact holes, gate (G), S, D electrodes were formed by aluminum (Al) evaporation and wet etching. Post metallization annealing was performed at 250°C for 1 h in clean room air ambient.

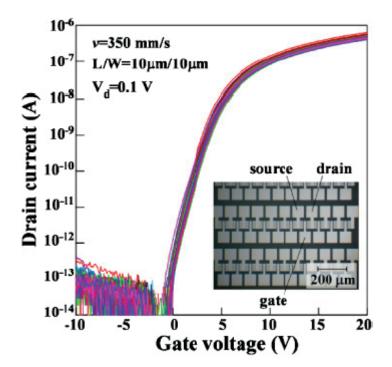

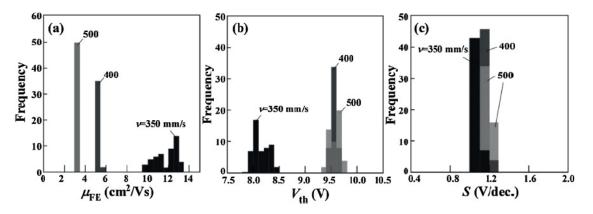

The transfer characteristics by 50 TFTs with channel length (*L*) and channel width (*W*) of 10 µm were measured. Figure 2.6 shows TFTs crystallized by v = 350 mm/s and the characteristics of  $\mu_{\text{FE}}$ , threshold voltage (*V*<sub>th</sub>), and swing factor (*S*) were summarized in Fig. 2.7. TFT performance was observed from output and transfer characteristics. When lower  $V_{\text{d}}$ , a trans-conductance ( $g_{\text{m}}$ ) and  $I_{\text{d}}$  can be described as [6]

$$g_m = \frac{\partial I_d}{\partial V_g} = \mu_{FE} \frac{W}{L} c_i V_d, \qquad (2.1)$$

$$I_{d} = \mu_{FE} \frac{W}{L} c_{i} (V_{th} - V_{g}) V_{d}.$$

(2.2)

Here, W and L are channel width and length, respectively. The  $c_i$  is capacitance per unit area of gate SiO<sub>2</sub>. By using Eqs. (2.1) and (2.2),  $\mu_{FE}$ ,  $V_{th}$ , sub-threshold swing value (S) can be estimated by equation as

$$\mu_{FE} = \frac{g_m}{\frac{W}{L}c_i V_d},\tag{2.2}$$

$$V_{th} = V_g - \frac{I_d}{\mu_{FE} \frac{W}{L} c_i V_d}.$$

(2.4)

Fig. 2.6. . Transfer characteristics of 50 TFTs superimposed in the graph. The inset shows a photograph of the TFTs [5].

Fig. 2.7. Histograms of characteristics of TFTs fabricated with v = 350, 400, and 500 mm/s.[5]

$$S = \ln 10 \frac{\partial V_g}{\partial \ln I_d}.$$

(2.5)

By decreasing v, the average  $\mu_{FE}$  increased from 3.3 to 12.1 cm<sup>2</sup>/Vs. At v = 350 mm/s, the variation in  $\mu_{FE}$ ,  $V_{th}$ , and S were within 1.06 (± 4.4%), 0.14 (± 1.1%), and 0.04 (± 4.0%). These small variations were achieved because SPC-Si films were formed by microcrystalline Si ( $\mu$ c-Si) with the size of ~20 nm. These results indicate that TPJ crystallization of a-Si film is quite promising for fabrication of TFTs.

#### 2.2 Noncontact temperature measurement of TPJ

#### irradiation

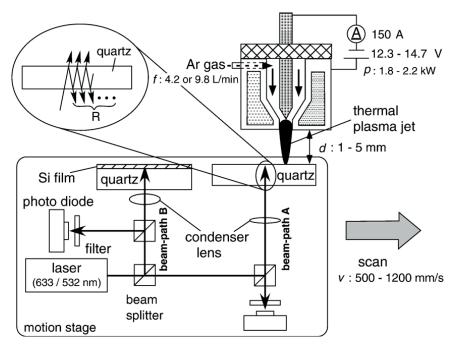

We have developed a direct observation technique for the temperature distribution in the quartz substrate during TPJ irradiation [7-8]. A transient reflectivity measurement was applied to measure the temperature as shown in Fig. 2. 8. The transient reflectivity during TPJ annealing was measured by irradiating the quartz substrate with a He-Ne laser (633 nm) from backside of the substrate and detecting the reflected light intensity using a photodiode through a band pass filter (root A in Fig. 2.18). Root B using an yttrium aluminum garnet (YAG) laser (532 nm, 10 mW) was used to investigate phase transformation of Si films. The transient reflectivity is oscillated by the interface of the incident light multiply reflected as shown in the inset of Fig. 2.8. The oscillation was reproduced by numerical simulations on heat diffusion and optical interference. The simulation has been based on two-dimensional heat diffusion equation shown as

$$\frac{\partial T}{\partial t} = \frac{\kappa}{\rho c_p} \left( \frac{\partial^2 T}{\partial x^2} + \frac{\partial^2 T}{\partial y^2} \right) + \frac{s}{\rho c_p} - \alpha (T - T_0) .$$

(2.6)

Here, x and y are positions along TPJ scanning direction and depth from substrate surface, respectively. Temperature (T) at each position and time (t) is obtained from Eq. 2.6 using

Fig. 2. 8. Schematic diagram of experimental set up for the temperature measurement. The optical beam paths A and B are used to measure the temperature profile in the substrate and phase transformation of Si films, respectively. [7]

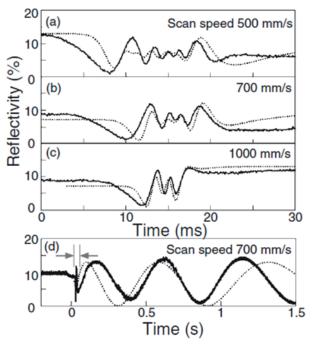

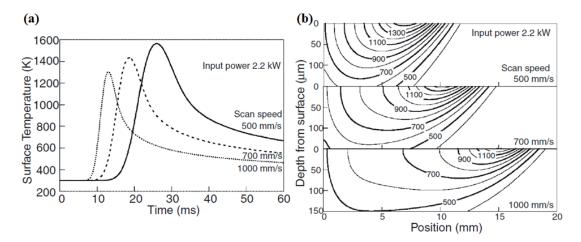

thermal conductivity ( $\kappa$ ), density ( $\rho$ ), and specific heat ( $c_p$ ) of quartz with considering temperature dependence. *S*,  $\alpha$ , and  $T_0$  are the thermal incidence, heat dissipation factor and ambient temperature, respectively. Then, the TPJ profile has been assumed by two-dimensional Gaussian power profiles, and the TPJ width and effective power transfer efficiency to quartz substrate ware used as parameters for fitting the numerical and experimental data. Two transient reflectivity measured and simulated with different v were shown in Fig. 2.19. From the figure, simulated reflectivity corresponded with measured reflectivity at all v. At the simulation, surface temperature and temperature distribution can be reproduced well as shown in Fig. 2.10. The substrate surface temperature increased with the decrease in v, and heated depth over 1000 K was within several 10  $\mu$ m in this experiment. The margin of error by this temperature measurement technique is less than 30 K, which is confirmed by the comparison between temperature and transient reflectivity of Si film measured from root B in Fig. 2.18 [7]. In, addition, this technique has been also applied to Si wafer and conventional glass substrate [9-10].

Fig. 2.9. Measured transient reflectivity (solid lines) and simulated reflectivity (dotted lines) of quartz substrate when plasma jet was scanned at different v. A long-term oscillation is shown in (d), where the period indicated by arrows corresponds to the period in (a) to (c). [7]

Fig. 2.10. (a) Surface temperature and (b) two-dimensional temperature profile under different annealing conditions obtained by analysis. The numerals indicate temperatures in the unit of K. [7]

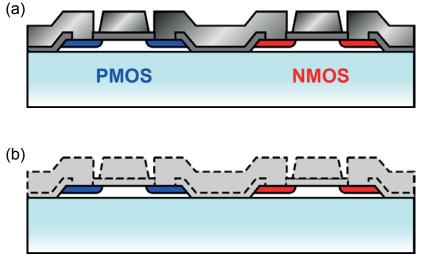

## 2.3 Fabrication of NMOS and PMOS TFTs

Fig. 2.11. The process steps for fabrication of NMOS and PMOS TFT using ion implantation and TPJ crystallization.

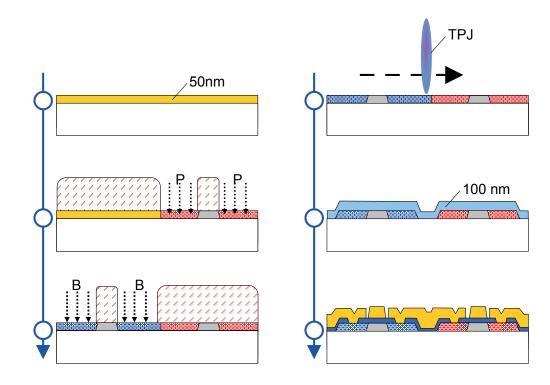

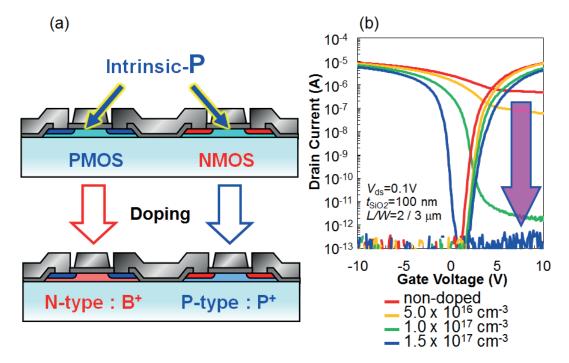

In order to fabricate CMOS circuit, both of NMOS and PMOS should be fabricated on the same substrate. In this section, NMOS and PMOS characteristics by TPJ crystallization were investigated. The process steps were modified as follows (Fig. 2.11)

In order to distinguish NMOS and PMOS region, impurity doping method by ion implantation was applied instead of depositing a doped-Si film. A 50-nm-thick non-doped a-Si was formed on quartz substrate by PECVD at 250°C. Using photolithography, Phosphorus (P<sup>+</sup>) and Boron (B<sup>+</sup>) ions were implanted at the dose of  $3.2 \times 10^{15}$  cm<sup>-2</sup> on the S/D areas of NMOS and PMOS regions, respectively. Then TPJ was irradiated to crystallize channel region and to activate S/D region, simultaneously. TPJ condition was *f* = 7.0 L/m, *d* = 3 mm, *P* = 2.25 kW, and *v* = 350 mm/s. After formation of TFT pattern with S/D and C by CDE, gate SiO2 with the thickness of 100 nm was formed by remote-PECVD at 300°C. After formation of contact holes, Al-Si (1%) electrodes were formed by DC sputtering and wet etching. Finally, PMA was performed at 250°C in the clean room air ambient. The highest temperature of this process steps was 400°C during a-Si deposition.

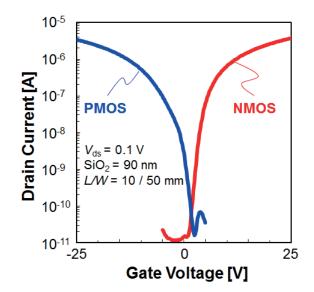

As shown in Fig. 2.12, NMOS and PMOS TFTs were successfully operated. The  $\mu_{\text{FE}}$  and

Fig. 2.12. Transfer characteristics of NMOS and PMOS TFTs using TPJ crystallization.

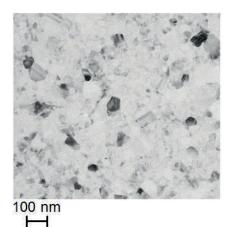

Fig. 2.13. Plane-view TEM image of crystallized Si film with v = 350 mm/s.

$V_{\rm th}$  were 19 cm<sup>2</sup>/Vs and 11 V by NMOS, respectively. They were 17 cm<sup>2</sup>/Vs and 11 V by PMOS, respectively. From these results, TPJ crystallization was promising for CMOS operation on glass substrate. Figure 2.13 shows plane-view transmission electron microscopy of crystallized Si film with v = 350 mm/s. In this TPJ condition, grains with the size from 50 to 100 nm were easily formed by SPC. However, LPC condition was hardly controlled because molten Si film was almost stripped or agglomerated.

Unfortunately, however, taking account of practical application to CMOS circuit operation, higher  $\mu_{FE}$  and lower  $V_{th}$  are strictly required. Enlargement of grain size is one of the research purpose to improve these TFT performance. So a new crystallization method using plasma induced annealing to form higher crystallinity Si, such as LPC, was required.

# 2. 4 High-speed lateral crystallization by micro-thermal

# plasma jet irradiation

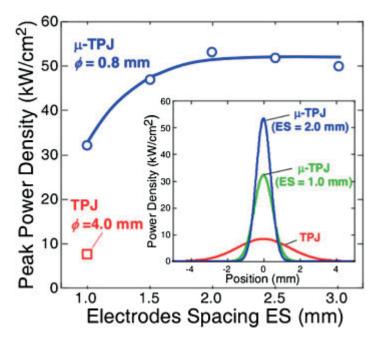

In order to fabricate higher performance TFTs using TPJ technique, the method to achieve high power density plasma was introduced [11 - 12]. Figure 2.14 shows the special profiles of TPJ and introduced micro-TPJ ( $\mu$ -TPJ). By reducing ( $\Phi$ ) and increasing the spacing between anode and cathode (*ES*), the power density was further increased. The FWHM and the power profile were reduced from 3.4 to 1.2 mm and the peak power density transferred to a substrate increased from 8.3 to 53.2 kW/cm<sup>2</sup> by decreasing  $\Phi$  from 4.0 to 0.8 mm and increasing *ES* from 1.0 to 2.0 mm. These results suggest that the  $\mu$ -TPJ can efficiently anneal the substrate surface by transmitting the heat by high-temperature gas stream with high power density.

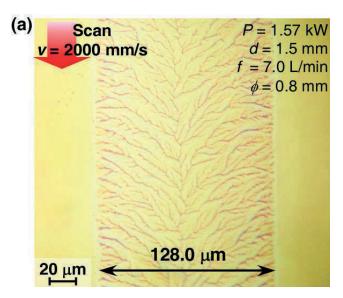

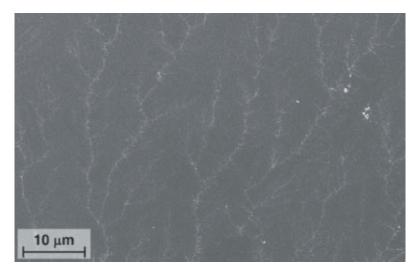

Figure 2.15 shows the application of  $\mu$ -TPJ to crystallization of a-Si film. A 100-nm thick a-Si film was crystallized by  $\mu$ -TPJ irradiation with v = 2000 mm/s after dehydrogenation. By optical microscope observation, dendritic morphology was observed, which indicates the grain growth by lateral solidification after phase transformation of liquid phase. By scanning electron microscope observation after secco etching, the grain size was ~5  $\mu$ m in the width and ~60  $\mu$ m in the length (Fig. 2.16). These large grains were formed by a strong lateral temperature gradient by high speed scanning speed of melting region. Therefore, we

Fig. 2.14. Peak power density transferred from plasma jet to substrate surface as a function of *ES* from 1.0 to 2.0 mm and  $\Phi$  from 4.0 to 0.8 mm during TPJ or  $\mu$ -TPJ irradiation. [11]

Fig. 2.15. Optical microscope image of Si film after  $\mu$ -TPJ irradiation with HSLC condition [12].

Fig. 2.16. SEM image of crystallized Si film using  $\mu$ -TPJ irradiation after secco etching [12].

called this growth method high-speed lateral crystallization (HSLC).

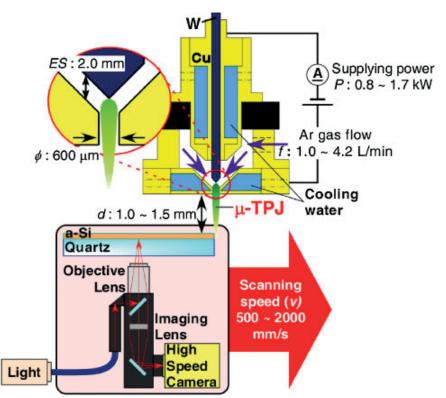

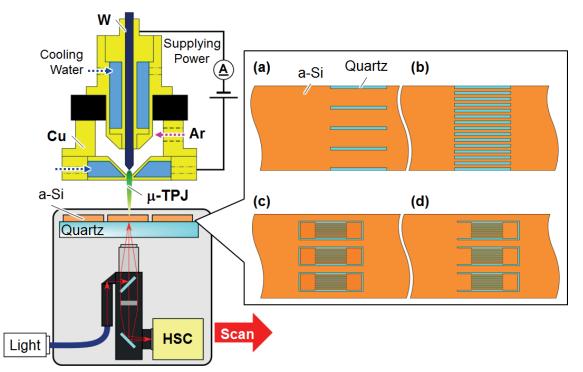

Moreover, the grain growth during  $\mu$ -TPJ irradiation was investigated by *in-situ* observation using high-speed camera (HSC) [13 - 14]. Figure 2.17 shows the schematic diagram of *in-situ* observation during  $\mu$ -TPJ irradiation on a-Si film. A 100-nm thick a-Si film was formed on quartz substrate by PECVD at 250°C. Then dehydrogenation was carried out at 450°C for 1h. The  $\mu$ -TPJ was generated under atmospheric pressure with P = 1.1 kW, d = 1.5 mm, f = 2.8 L/min, and v = 800 mm/s. For *in-situ* observation of grain growth, an optical microscope and an HSC were set on the motion stage in the backside of the substrate. The frame rate ( $f_r$ ) was set to 1600 frames per second (fps).

Fig. 2.17. Schematic diagram of *in-situ* observation during µ-TPJ irradiation.

Fig. 2.18. Snapshot of the high-speed camera movie during  $\mu$ -TPJ irradiation. After phase transformation from a-Si, SPC to LWC, HSLC was formed from molten region (MR) [13].

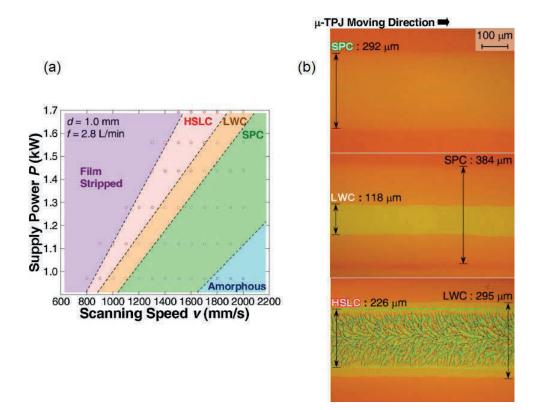

Fig. 2.19. (a) Crystallization mode with respect to  $\mu$ -TPJ crystallization condition by *P* and *v*. (b) Optical microscope images of SPC, LWC and HSLC, respectively [14].

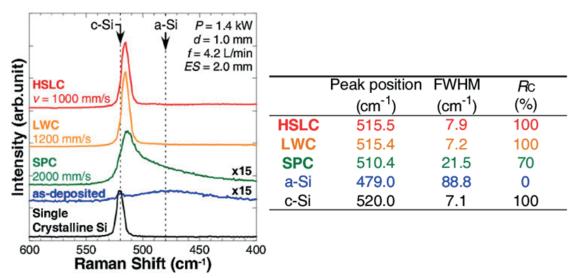

Fig. 2.20. Peak position and FWHM of c-Si TO phonon peak and crystallinity of crystallized Si films shown in Fig. 2. 19[14].

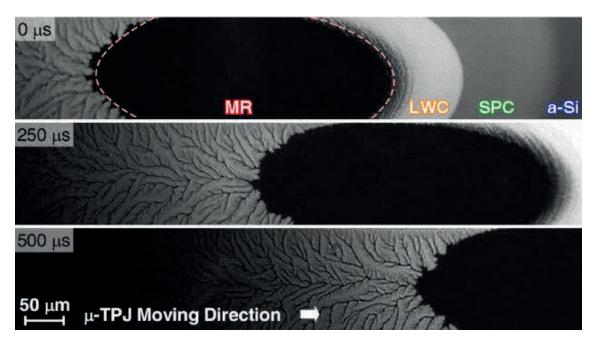

Figure 2.18 shows the snapshot by HSC. The molten region was observed as black due to high reflectivity of liquid-Si (*l*-Si). In front of the molten region, the transformation from

Fig. 2.21. Transfer characteristics of TFTs on (a) quartz substrate and (b) glass with buffer  $SiO_2$  layer substrate [16].

a-Si, SPC, to periodic and repeating wavy crystallization were observed. The explosive crystallization (EC) [15] like mode was named leading wave crystallization (LWC) [13-14]. The driving force of EC is generally the released latent heat at the liquid-amorphous interface [13-15]. In the case of LWC, EC propagates into SPC region, which has less latent heat because the melting point of a-Si and SPC-Si is different [13-14].

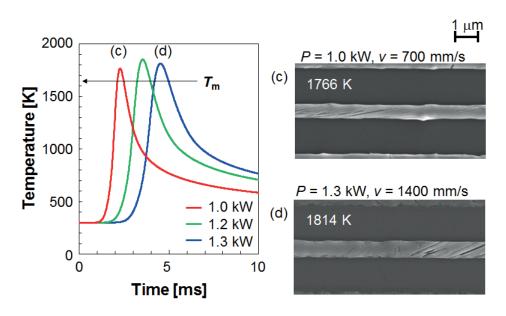

As shown in Figs. 2.19(a) and (b), the crystallization modes of SPC, LWC and HSLC were successfully controlled by the combination of P and v. The crystalline volume fractions of each crystallization mode were estimated from Raman scattering spectra, as shown in Fig. 4.20. The SPC shows a crystalline volume fraction ( $R_c$ ) of almost 70%. This result suggests that a substantial amount of a disordered structure or amorphous component remains in the SPC region. On the other hand, both of LWC and HSLC showed an  $R_c$  of almost 100%. These results suggest that the melting points of LWC- and HSLC-Si are identical to that of single-crystalline Si ( $T_m$ ). From these results we concluded that HSLC is induced by melting almost single crystalline Si after phase transformation of SPC and LWC.

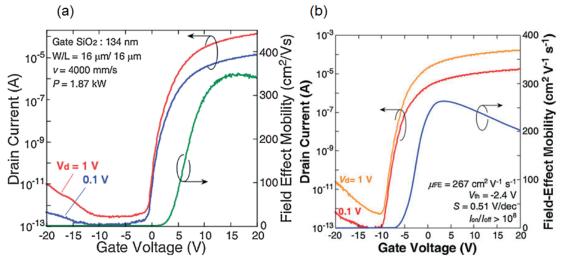

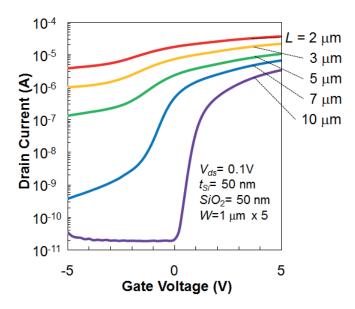

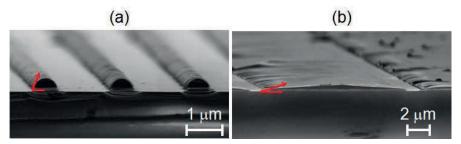

Furthermore,  $\mu$ -TPJ crystallization with HSLC was applied to TFT fabrication [10, 16]. In order to demonstrate its practicability, TFTs were fabricated on quartz and glass substrate. Figure 2.21(a) shows the transfer characteristics of NMOS TFT fabricated by HSLC film on quartz substrate. TFT showed extremely high  $\mu_{FE}$  of 350 cm<sup>2</sup>/Vs and low *S*. On the other hand in the case of glass substrate, the crack generation was frequently occurred by HSLC of a-Si film on glass substrate. However, they were significantly suppressed by the inter SiO<sub>2</sub> buffer layer between a-Si and substrate. As shown in Fig. 2.21(b), TFT with high  $\mu_{FE}$  of 267 cm<sup>2</sup>/Vs was successfully fabricated on glass substrate with 500 nm thick

of SiO<sub>2</sub> buffer layer.

From these results,  $\mu$ -TPJ crystallization technique is quite promising for high-performance TFT fabrication because of its practicability with low cost and low temperature process.

# References

- H. Kaku, S. Higashi, H. Taniguchi, H. Murakami, and S. Miyazaki, Appl. Surf. Sci. 244, 8 (2005).

- [2] S. Higashi, H. Kaku, H. Taniguchi, H. Murakami, and S. Miyazaki, Thin Solid Films 487, 122 (2005).

- [3] S. Higashi, H. Kaku, H. Murakami, S. Miyazaki, and H. Wakatabe, Jpn. J. Appl. Phys. 44, L108 (2005).

- [4] T. Yorimoto, S. Higashi, H. Kaku, T. Okada, H. Murakami, S. Miyazaki, T. Matsui, A. Masuda, and M. Kondo, Jpn. J. Appl. Phys. 47, 6949 (2008).

- [5] S. Higashi, K. Sugakawa, H. Kaku, T. Okada, and S. Miyazaki, Jpn. J. Appl. Phys. 49, 03CA08 (2010).

- [6] Thin film materials and devices meeting, Hakumaku Transistor (Thin-Film Transistor) (Corona Publishing Co., Ltd., Tokyo, 2008) [in Japanese].

- [7] T. Okada, S. Higashi, H. Kaku, N. Koba, H. Murakami, and S. Miyazaki, Jpn. J. Appl. Phys. 45, 4355 (2006).

- [8] T. Okada, S. Higashi, H. Kaku, N. Koba, H. Murakami, and S. Miyazaki, Thin Solid Films 515, 4897 (2007).

- [9] K. Tanaka, S. Hayashi, S. Morisaki, and S. Higashi, Jpn. J. Appl. Phys. 54, 01AE05 (2014).

- [10] H. Furukawa, S. Higashi, T. Okada, H. Kaku, H. Murakami, and S. Miyazaki, Jpn. J. Appl. Phys. 47, 2460 (2008).

- [11] S. Hayashi, S. Higashi, H. Murakami, and S. Miyazaki, Appl. Phys. Express 3, 061401 (2010).

- [12] S. Higashi, S. Hayashi, Y. Hiroshige, Y. Nishida, H. Murakami, and S. Miyazaki, Jpn. J.Appl. Phys. 50, 03CB10 (2011).

- [13] S. Hayashi, Y. Fujita, T. Kamikura, K. Sakaike, M. Akazawa, M. Ikeda, H. Hanafusa, and S. Higashi, Appl. Phys. Lett. 101, 172111 (2012).

- [14] S. Hayashi, Y. Fujita, T. Kamikura, K. Sakaike, M. Akazawa, M. Ikeda, and S. Higashi: Jpn. J. Appl. Phys. 52, 05EE02 (2013).

- [15] J. S. Im, M. A. Crowder, R. S. Sposili, J. P. Leonard, H. J. Kim, J. H. Yoon, V. V. Gupta,H. Jin Song, and H. S. Cho, Phys. Status Solidi A 166, 603 (1998).

- [16] Y. Fujita, S. Hayashi, and S. Higashi, Jpn. J. Appl. Phys. 51, 02BH05 (2012).J. Nishii, F. M. Hossain, S. Takagi, T. Aita, K. Saikusa, Y. Ohmaki, I. Ohkubo, S. Kishimoto, A. I. Ohtomo, T. Fukumura, F. Matsukura, Y. Ohno, H. Koinuma, H. Ohno and M. Kawasaki, Jpn. J. Appl. Phys. 42 (2003) 347.

# Chapter 3

# Improvement of Characteristic Variability in TFTs by Micro Thermal Plasma Jet irradiation on Amorphous Silicon Strips

# 3.1 Introduction

As described in Sect 2.1, grains larger than ~60  $\mu$ m were formed by high-speed lateral crystallization (HSLC) using micro-thermal-plasma-jet ( $\mu$ -TPJ) irradiation. In addition, we have demonstrated a high field effect mobility of 350 cm<sup>2</sup>/Vs with HSLC by a high scanning speed ( $\nu$ ) of 4000 mm/s [1]. However, random grain boundaries (GBs) were formed by HSLC on continuous amorphous silicon (a-Si) films. Random GBs cause characteristic variability in thin film transistors (TFTs)[2 - 4]. So the improvement of characteristic variability of TFTs is one of the greatest challenge for crystalline silicon (c-Si) TFTs. For this variability issues, we have attempted to control the grain growth by  $\mu$ -TPJ crystallization of a-Si pattern. This method is very simple and easy to apply TFT fabrication without additional process steps.

In this section, we concluded that  $\mu$ -TPJ irradiation on a-Si strip patterns was quite effective to control grain growth and a new TFT channel pattern is proposed. Additionally, we improved variability in TFTs and attempted to operate CMOS circuits at low supply voltage.

# 3.2 Experimental procedure

## 3.2.1 Grain growth control using a-Si strip patterns

The a-Si films with a thickness of 50 nm were formed on quartz substrates by plasma-enhanced chemical vapor deposition (PECVD), followed by dehydrogenation at 450 °C for 1 hour. Subsequently, a-Si patterns were formed by chemical dry etching (CDE). μ-TPJ source used for the crystallization of a-Si films is schematically shown in Fig. 3.1. Thermal plasma was generated by DC arc discharge under atmospheric pressure with supplying DC power (P) of 1.6 kW between the anode and cathode electrodes with the spacing (ES) of 2.0 mm with an Ar gas flow (f) of 3.0 L/min. The  $\mu$ -TPJ was formed by blowing out the arc plasma through an orifice ( $\Phi$ ) of 0.6 mm in diameter. The distance to the substrate was kept at 1.5 mm away from the plasma source and the substrate was linearly translated in front of the µ-TPJ with a scanning speed at 1600 mm/s. In this condition, ~100 µm wide molten zone is formed and rapid lateral re-crystallization was induced by the rapid movement of molten Si. Here, we formed several a-Si patterns. First, lines and spaces from 1 to 10 µm wide patterns were formed. Their crystallinity was investigated by scanning electron microscope (SEM) after secco etching. From these results, a new TFT pattern for location control of grain growth was proposed. Two types of TFT patterns were formed to evaluate grain growth in a-Si pattern: (1) conventional TFT

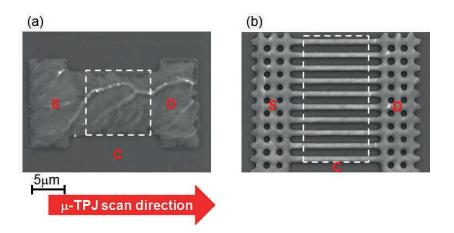

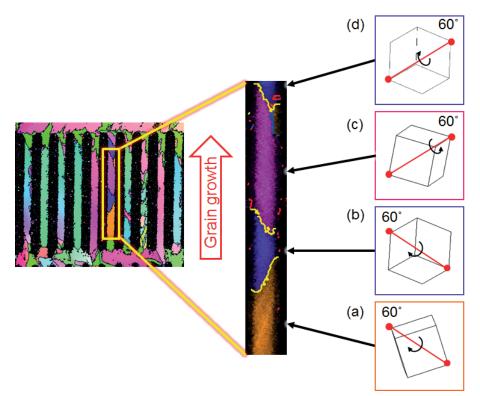

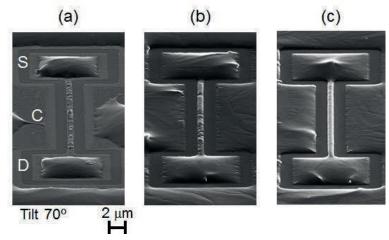

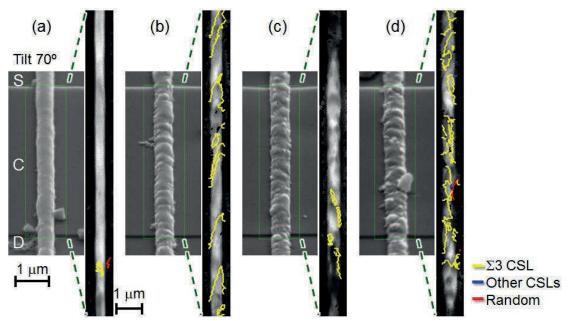

Fig. 3.1. schematic diagram of  $\mu$ -TPJ irradiation on on a-Si patterns. (a) conventional TFT pattern with  $L/W = 10/10 \mu m$ , and (b) 1  $\mu$ m-wide strip TFT pattern with  $L/W = 10/1 \times 10$  lines.

pattern with the channel length (*L*) and width (*W*) of 10  $\mu$ m is shown in Figs. 1(a) and (2) our proposed pattern with *L* = 10  $\mu$ m and *W* = 1  $\mu$ m times 10 lines is shown in Fig.1(b), respectively. The proposed pattern was formed by 1 $\mu$ m wide strips, not only in the channel area but also in the source and drain area. For evaluation, crystallographic orientations and GBs were investigated by the electron-backscattering-diffraction (EBSD) method.

#### 3.2.2 In-situ observation of grain growth in a-Si patterns during

### μ-TPJ irradiation

Un-doped a-Si film with the thickness ( $t_{Si}$ ) of 100 nm was formed on quartz substrate by plasma-enhanced chemical vapor deposition (PECVD) using SiH<sub>4</sub> and H<sub>2</sub> at 250°C. Dehydrogenation was carried out in N<sub>2</sub> ambient at 450°C for 1 hour. Then a-Si was patterned by chemical dry etching (CDE).  $\mu$ -TPJ was generated by DC arc discharge under

Fig. 3.2. The schematic diagram of experimental set up for the in-situ observation of grain growth during  $\mu$ -TPJ irradiation on a-Si patterns. The observed patterns are as follows: slit patterns with (a)  $W = 10 \mu m$  and (b)  $W = 3 \mu m$ , and (c) isolated and (d) continuous TFT patterns with 1  $\mu m$  wide strip channel.

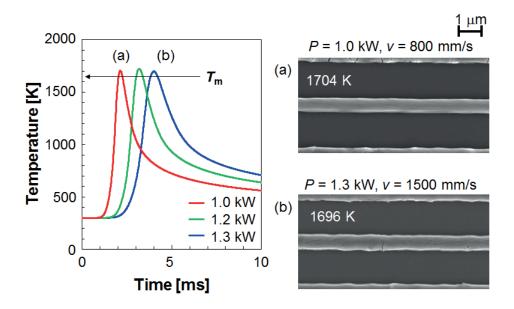

atmospheric pressure with a supplying power (*P*) of 1.1 - 1.3 kW between a W cathode and Cu anode separated by 2.0 mm. The Argon gas flow rate (*f*) was 1.0 L/min.  $\mu$ -TPJ was formed by blowing out the thermal plasma through an orifice with a diameter of 600  $\mu$ m. The substrate was linearly moved by a motion stage in front of the  $\mu$ -TPJ with a scanning speed (*v*) ranging from 800 to 1600 mm/s. The distance between the plasma source and substrate (*d*) was kept at 1.0 mm. For the *in-situ* observation of grain growth of a-Si patterns during  $\mu$ -TPJ irradiation, an optical microscope and an high-speed camera (HSC) were set on the motion stage in back of the substrate (Fig. 3.2) [5 - 6]. The frame-rate (*R*<sub>f</sub>) was varied from 25000 to 50000 frames per second (fps).

The a-Si patterns used in this experiment are schematically shown in Figs. 3.2(a) to (c). First, slit patterns with 10  $\mu$ m and 3  $\mu$ m were formed in order to compare grain growth with respect to pattern width (Figs. 3.2(a) and (b)). Secondly, the application of strip pattern to TFTs was investigated. Taking into account of fabrication process steps, it is practical to crystallize isolated patterns with source (S), channel (C) and drain (D) of TFT. In this work we defined TFT pattern as an isolated pattern with S, C, and D in the Si layer. For comparison, we formed isolated and continuous TFT patterns (Figs. 3.2(c) and (d)), and grain growth was observed. After crystallization of these patterns, crystallographic orientation and the kind of grain boundaries in observed area were investigated by EBSD.

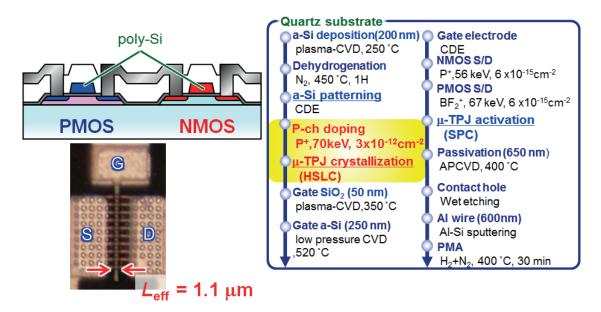

#### 3.2.3 Fabrication of CMOS-TFTs with strip channel

We fabricate CMOS TFTs with the self-aligned top-gate structure. First, the a-Si film with a thickness of 50 nm is formed on guartz substrate by PECVD at 230 °C, followed by dehydrogenation at 450°C in N<sub>2</sub> ambient for 1 h. The channel (C), source (S), and drain (D) are patterned by photolithography and CDE as shown in Figs. 3. 1(a) and (b). Then, a-Si patterns were crystallized only in the area of TFTs by µ-TPJ irradiation in order to increase throughput of fabrication process. The a-Si patterns were crystallized under same condition of above mentioned. Subsequently, the gate-SiO<sub>2</sub> with a thickness of 50 nm was deposited by remote PECVD at 300 °C [7], and poly-Si gate electrode with a thickness of 250 nm was formed by low pressure CVD (LPCVD) at 520 °C. The gate electrodes were patterned using photolithography and CDE. Afterwards, the photoresist was used as an implantation mask for NMOS and PMOS regions, respectively. Then 6.2×10<sup>15</sup> cm<sup>-2</sup> phosphorus ions and boron ions were implanted at 55 and 67 keV, respectively, to form the self-aligned gate (G), S, and D. Next, the  $\mu$ -TPJ is used to activate dopants [8 - 9], with P = 1.5 kW and v = 2000 mm/s. Under this condition, Si films were not melted, rather, dopant activation was achieved by rapid annealing [10]. After formation of the 650 nm passivation layer by atmospheric pressure CVD (APCVD), the contact holes were formed

by photolithography and wet etching. Al-Si (1%) wires were formed by DC sputtering and patterned by photolithography and wet etching. Finally, CMOS transistor fabrication was completed by high pressure  $H_2O$  vapor annealing (HWA) at 260°C in 1 MPa for 6 h [11 -12]. The maximum temperature of fabrication process was 520°C in gate a-Si deposition.

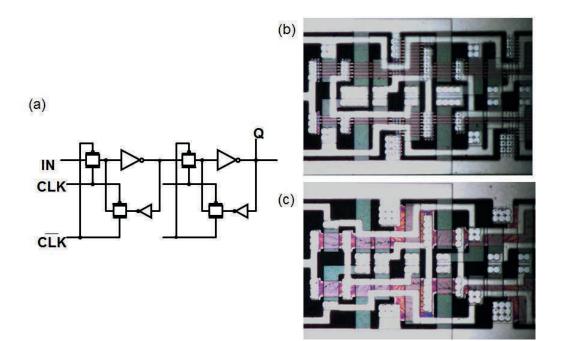

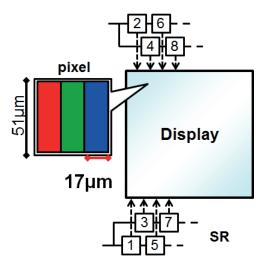

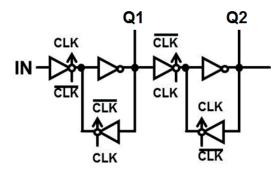

# 3.2.4 Operation of CMOS circuits with strip pattern TFTs

CMOS Circuit was also fabricated by the process steps shown in Sect. 3.2.1. In order to demonstrate industrial applications, shift register (SR), which is which is one of the key circuits for the peripheral driver of displays [13 - 15], was formed with conventional and strip pattern TFTs. CMOS circuit operation at a low supply voltage of 5V was targeted with the object of external interface. For the evaluation of circuits, a data generator (Tektronix: DG 2020A) and an active prove of 0.1 pF (GGB industries: model 12C) were used.

# 3.3 Results and discussion

# 3.3.1 Grain growth induced by µ-TPJ irradiation on a-Si pattern

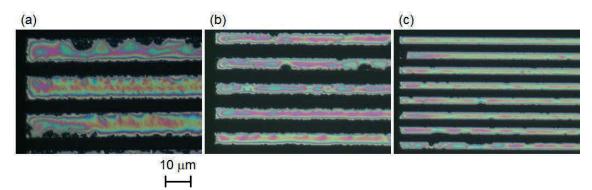

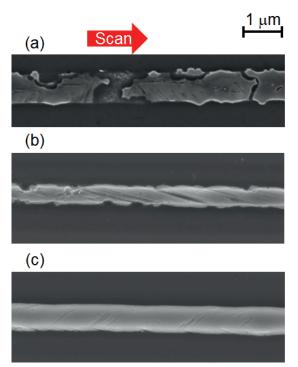

Firstly, we observed the crystallinity with respect to pattern width. As shown in Fig. 3.3, all patterns seemed to be crystallized by HSLC condition. In the case of  $10-\mu m$  wide pattern, the pattern shapes were frequently broken up (Fig. 3.3(a)). On the other hand, by

Fig. 3.3. Optical microscope images of crystallized Si patterns with the width of (a) 10  $\mu$ m, (b) 5  $\mu$ m, and (c) 3  $\mu$ m.

Fig. 3.4. The birds eye view SEM images of crystallized Si patterns with (a) continuous film and the lines with the width of (b) 10  $\mu$ m, (c) 5  $\mu$ m, and (d) 1  $\mu$ m after secco etching.

Fig. 3.5. An optical microscope image of strip and conventional TFT patterns after  $\mu$ -TPJ irradiation. Continuous film and conventional pattern were drastically agglomerated.

Fig. 3.6 SEM images of (a) conventional pattern with L/W=10/10  $\mu$ m and (b) strip pattern with L/W=10/1  $\mu$ m × 10 lines after  $\mu$ -TPJ crystallization..

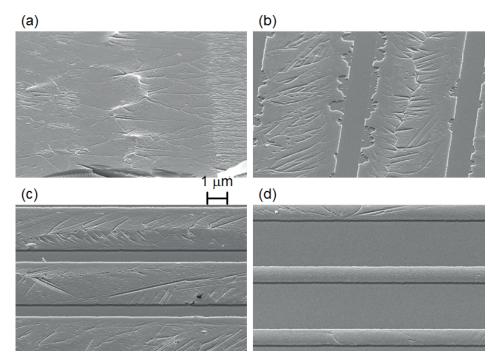

decreasing pattern width to 3  $\mu$ m, the deformations of pattern shape were obviously reduces. So we investigated the defect formation in each patterns. Figure 3.4 shows the bird's-eye view SEM images. As shown in Figs. 3.4(a) and (b), many GBs were formed in continuous film and 10-  $\mu$ m-wide patterns. In the case of 5- $\mu$ m-wide patterns, GBs were still formed but were reduced in some patterns (Fig. 3.4(c)). By reducing the width to 1  $\mu$ m, GBs were obviously reduced and no GBs were formed in some patterns (Fig. 3.4(d)). These results suggest that narrow strip pattern is quite effective to suppress the formation of GBs and deformation of pattern shape. So we proposed a new TFT pattern, which is consisted of 1  $\mu$ m-wide strips. As shown in Fig. 3.5, while continuous film and conventional TFT patterns were drastically broken up by  $\mu$ -TPJ irradiation with high-*P*

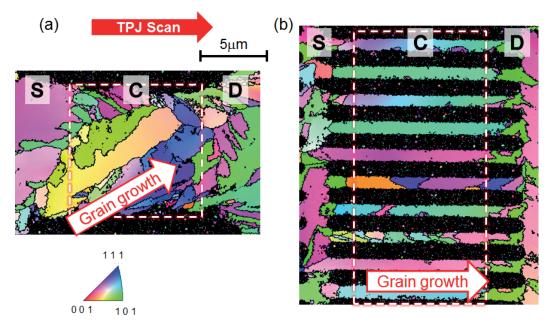

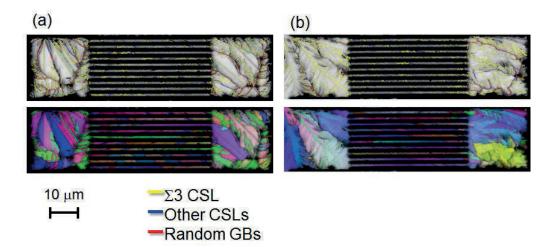

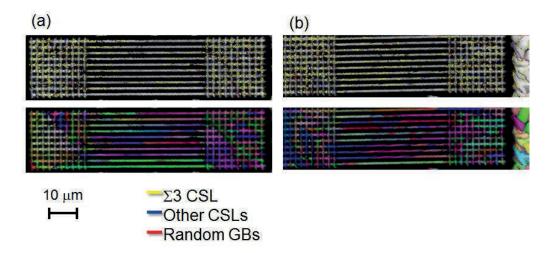

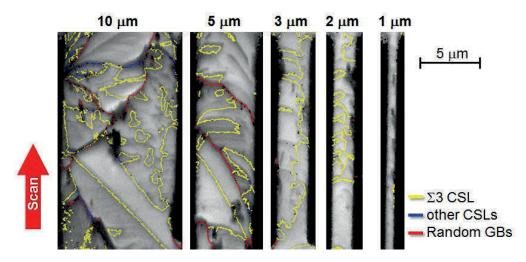

Fig. 3.7 Inverse Pole Figure (IPF) map from surface direction of (a) conventional and (b) strip pattern. The scan direction of  $\mu$ -TPJ was from left to right, and the center was upper side of both figures.

Fig. 3.8 GBs formed in (a) conventional and (b) strip pattern. Red, blue and yellow lines show random GBs, CSLs from 5 to 19 and  $\Sigma$ 3 CSLs, respectively.

condition, all of the proposed strip TFT patterns retained their original shape. From these results, strip TFT pattern is quite promising to suppress the formation of GBs and to improve process window of  $\mu$ -TPJ crystallization.

So we investigated the application of strip TFT pattern compared to conventional TFT pattern (Fig. 3.5(a) and (b)). The crystallographic orientations in the channel region with

conventional and strip pattern were investigated by EBSD. As shown in Fig. 3.7(a), the growth direction of grains was tilted. The grains grow with a slope according to thermal gradient and scan direction of  $\mu$ -TPJ [1], and GBs crossed the channel region in

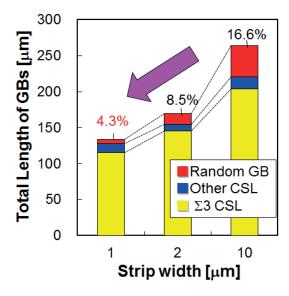

Fig. 3.9 Total length of GBs in 10  $\mu$ m × 10  $\mu$ m area with respect to strip width. Red, blue and yellow lines show random GBs, CSLs from 5 to 19 and  $\Sigma$ 3 CSLs, respectively.

Fig. 3.10 IPF map with GBs of 6th line in Fig. 3.7(b). The lattice of (111) axis and rotation axis of each grains are shown in (a) to (d).

conventional pattern. Thus, in the conventional pattern, grain growth was tilted against the source-drain direction, because of thermal gradient, which is the highest in the center, and the scan direction of  $\mu$ -TPJ. On the other hand, in strip pattern, grain growth direction is controlled by the strip direction and GBs are filtered out by the strip pattern as shown in Fig. 3.7(b). In addition, single-grain growth was observed in some strips.

Secondly, we investigated the GBs in both patterns. Figure 3 shows  $\sum 3$  coincidence site lattice (CSL) with yellow, other CSLs with blue, which were CSLs from 5 to 19, and random GBs with red, respectively. In the case of conventional pattern, random GBs and CSLs [16 - 19] were formed in the channel area, as shown in Fig. 3.8(a). On the other hand in the strip pattern, GBs were clearly reduced and random GBs were mostly stopped in front of channel area, as shown in Fig. 3.8 (b). Figure 3.9 shows the total length of GBs in  $10 \times 10 \ \mu\text{m}^2$  area with respect to pattern width. All GBs in strip pattern were clearly

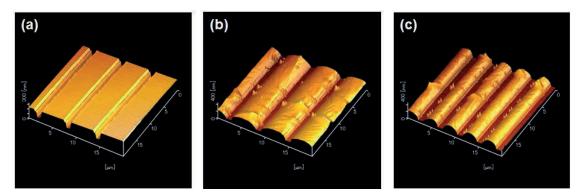

Fig. 3.11 Atomic Force Microscope (AFM) images of Si pattern (a) a-Si pattern of 5  $\mu$ m and (b), (c) after  $\mu$ -TPJ crystallization of 5 and 3  $\mu$ m, respectively.

Fig. 3.12 Raman peak position of crystallized Si patterns with respect to strip width.

reduced.

Random GBs were reduced to 4.3% and  $\sum 3$  CSLs were also reduced in the 1-µm strip pattern. This suggests that random GBs were eliminated out by the filtering effect of strips. However, CSLs were still formed in channel area of strip pattern. We found that GBs in the strip pattern were mostly  $\sum 3$  CSLs which are reported as electrically inactive [19-21] (Fig. 3.8(b)). Figure 3.10 shows unique grain growth of the 6th line in Fig. 3.8(b). All of these  $\sum 3$  CSLs were formed by 60° rotation around (111) axis. In the case of  $\sum 3$  CSL between Fig. 3.10(a) and (b), grain was rotated 60° around (111) axis. In the case between Fig. 3.10(b) and (c), the grain was rotated 60° around sthe other (111) axis and returned by counter rotation in next  $\sum 3$  CSL between Fig. 3.10(c) and (d). this grain growth suggests that narrow strips suppress the formation of random GBs and only limited crystallographic rotations such as  $\sum 3$  CSLs are allowed.

In addition, as shown in the atomic force microscope (AFM) image in Fig. 3.11, Si pattern shape is rounded at the upper side but interface between Si and substrate remained at the same position. The pattern shape become roundly by decreasing pattern width (Figs. 3.11 (b) and (c)) Figure 3.12 shows raman peak position as a function of channel width, which shows that tensile stress in narrow strip was clearly reduced [22]. These results suggest that the deformation of Si strips during the phase transformation plays a role to suppress random GB generation and preferential formation of CSL boundaries. It should be noted that there are no additional the process steps, such as capping layer formation for crystallization [18 - 19], which cause higher fabrication costs. The proposed strip channel TFT pattern s enable the suppression of random GBs by simple process steps.

## 3.3.2 In-situ observation of grain growth in a-Si patterns during

#### μ-TPJ irradiation

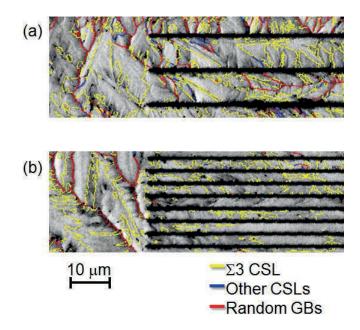

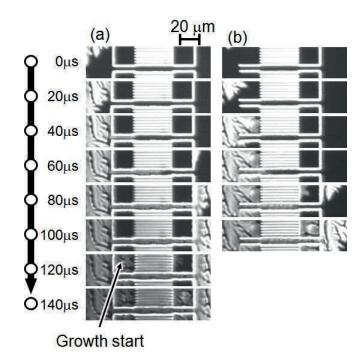

Grain growth in HSLC of amorphous silicon (a-Si) strips during  $\mu$ -TPJ irradiation is successfully observed by HSC. A-Si film was melted following solid phase crystallization (SPC) and leading wave crystallization (LWC) [5 - 6]. Figure 3.13 shows the snapshots with 32 µm wide area within the molten region ~ 100 µm. A liquid Si (*l*-Si) is observed in black because light from  $\mu$ -TPJ is obstructed by very high reflectivity of molten Si. After solidification, c-Si are shown in gray scale by transmitting the light and slit lines without a-Si film are shown in the brightest white. In the case without patterns, a number of dendritic growths were observed as shown in Fig. 3.13(a). The lateral growth was observed and nucleation was not observed. The growth direction of each dendritic growth was induced by scanning direction and thermal gradient of  $\mu$ -TPJ. In the case of 10 µm-wide

Fig. 3.13 Snap shots by HSC of HSLC on a-Si patterns during  $\mu$ -TPJ irradiation under the conditions of P = 1.3 kW, d = 1.5 mm, v = 800 mm/s, and  $f_r = 25000$  fps. 1  $\mu$ m-wide slits were formed by periods of (a) continuous film, (b) slit pattern with  $W = 10 \mu$ m, and (c) W = 3  $\mu$ m

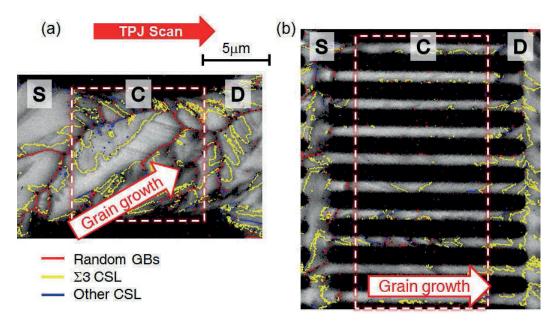

Fig. 3.14 GBs in crystallized patterns of (a)  $W = 10 \ \mu\text{m}$  and (b)  $W = 3 \ \mu\text{m}$  were drawn with superimposition on image quality (IQ) maps. These maps were observed at the same positions with Figs. 3.13 (b) and (c). Yellow, blue, and red lines express  $\Sigma$  3 CSL,  $\Sigma$  5 ~ $\Sigma$  19 CSLs, and random GBs, respectively.

pattern, no nucleation was occurred in the pattern edge and dendritic growth went into slit area. However, liquid-solid interfaces from both pattern edges collide with grain growth as shown in Fig. 3.13(b). On the other hand, in the case of 3 µm-wide pattern, single liquid-solid interface moved into each strips by controlling growth direction from left to right (Fig. 3.13(c)). Consequently, in order to compare the grain growth and formation of GBs, we investigated the GBs corresponding to observed patterns in Figs. 3.13(b) and (c). As shown in Fig. 3.14(a), random GBs with red line were formed in the place where grains collided. On the other hand, 3 µm-wide strips obviously suppressed the formation of random GBs. From these results, random GBs were suppressed by preventing collision of grains. However,  $\Sigma$  3 CSL was formed in both patterns. Because  $\Sigma$  3 CSL, which is electrically inactive, [19-21] was formed by rotating 60° around (111) axis as mentioned in Sect. 3.3.2, adjacent grains take over the crystallinity during solidification and formed no dangling bonds. So we concluded that narrow strip pattern forms high crystallinity by eliminating out the formation of random GBs. Moreover, we observed different condition of  $\mu$ -TPJ irradiation by decreasing v from 800 to 730 mm/s (Fig. 3.15). In this condition, the slit pattern was gradually agglomerated and the pattern shape was obviously transformed during melting period.

Fig. 3.14 Snap shots by HSC of HSLC on a-Si patterns with  $W = 10 \ \mu\text{m}$  during  $\mu$ -TPJ irradiation under the conditions of  $P = 1.3 \ \text{kW}$ ,  $d = 1.5 \ \text{mm}$ ,  $v = 750 \ \text{mm/s}$ , and  $f_r = 25000 \ \text{fps}$ .

Fig. 3.15 Snap shots by HSC of HSLC on TFT patterns during  $\mu$ -TPJ irradiation under the conditions of P= 1.1 kW, d = 1.0 mm, v = 1600 mm/s, and f = 50000 fps. (a) isolated and (b) continuous TFT patterns with 1  $\mu$ m-wide strip channel were formed.

**Table I.** Characteristics of *l*-Si on TFT pattern shown in Fig. 3.15.

|                          | w/o pattern | Isolated pattern | Continuous pattern |

|--------------------------|-------------|------------------|--------------------|

| Delay time (µs)          | 0           | 100              | 0                  |

| Growth velocity (m/s)    | 1.2         | 3.2              | 0.8                |

| Undercooling degree (°C) | ~100        | ~150             | ~90                |

Subsequently, we investigated the application of strip pattern to TFTs. Grain growth in TFT patterns as shown in Figs. 3.2(c) and (d) were observed. As shown in Figs. 3.15(a) and (b), in the case of isolated pattern, the continuous growth reached next to the TFT pattern at 20 $\mu$ s, however, the TFT pattern was fully melted and still in liquid phase. Solidification of TFT pattern at 120 $\mu$ s indicated the nucleation, delayed by 100  $\mu$ s compared with continuous pattern (Fig. 3.15 (b)). This is because the complete melting of TFT pattern lost the nucleus and the molten Si goes into undercooling condition. Once nucleation takes place at 120  $\mu$ s, rapid lateral solidification occur (with growth velocity of ~3.2 m/s). Here we considered about the reason that homogeneous nucleation, which results in defective grains [23 - 24], did not occur in spite of complete melting. As shown in Table I,  $\Delta T$  of 150°C and cooling rate of 5 × 10<sup>5</sup> K/s were estimated by growth velocity using Ref. 25. This slow cooling rate, compared with > 10<sup>10</sup> K/s by ELA [23 - 24], was achieved because  $\mu$ -TPJ heats Si patterns and the substrate simultaneously [26]. So

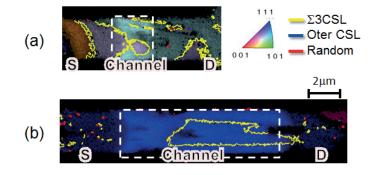

Fig. 3.16 GBs and crystallographic orientations of surface direction in crystallized patterns of TFT pattern were drawn with superimposition on image quality (IQ) maps. This map was observed at the same positions with Fig. 3.15 (a) and (b), respectively.

Fig. 3.17 GBs and crystallographic orientations of surface direction in crystallized patterns of TFT pattern were drawn with superimposition on image quality (IQ) maps. These patterns were composed of 1- $\mu$ m wide strip not only in channel but also S/D areas.

once nucleation occurred, lateral growth was induced by thermal gradient of  $\mu$ -TPJ in spite of homogeneous nucleation. In fact, as shown in Figs. 3.16 (a) and (b), random GBs are significantly suppressed in channel area as same as before. This grain growth was observed in the case of TFT patterns with lattice S/D as shown in Figs. 3.17 (a) and (b). These results indicate that we can grow crystalline Si without random GBs even in isolated TFT pattern with strip channel.

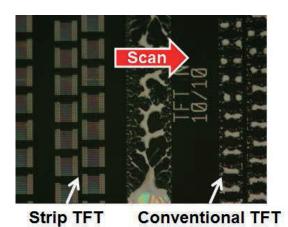

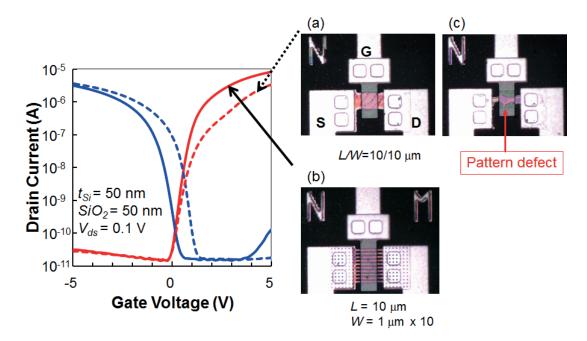

# 3.3.3 Self-aligned top gate CMOS TFT fabrication

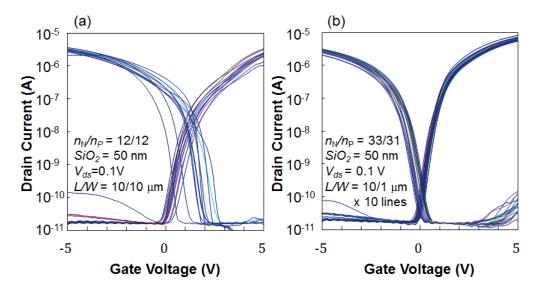

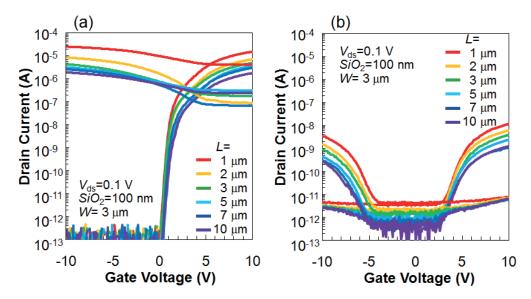

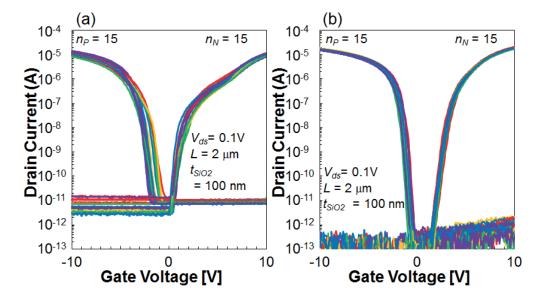

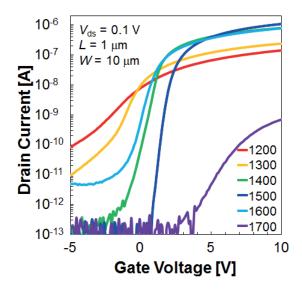

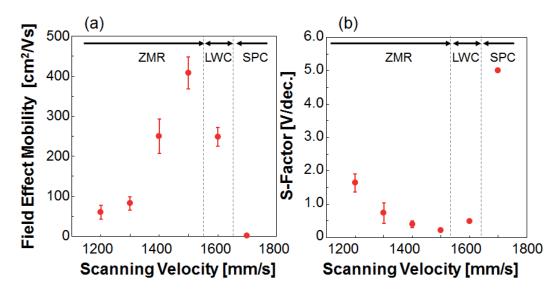

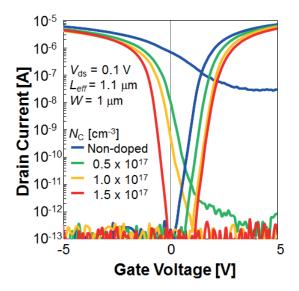

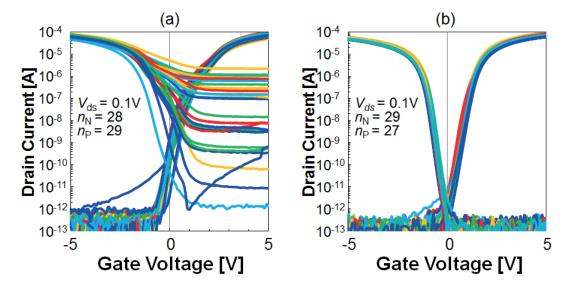

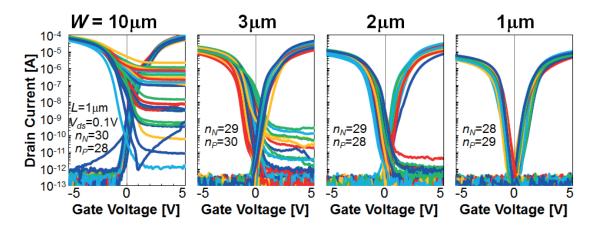

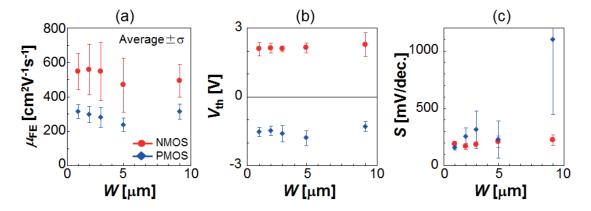

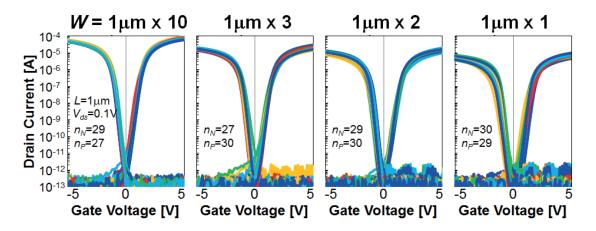

TFTs with conventional and strip channels were successfully fabricated as shown in Figs. 3.18(a) and (b). In the case of the conventional channel pattern, pattern defects frequently occurred due to agglomeration of molten Si during  $\mu$ -TPJ crystallization (Fig. 3.18 (c)). On the other hand in the strip pattern, pattern defects were markedly reduced and yield of TFT operation was improved. We could operate N-type and P-type TFTs with both patterns. TFTs with strip pattern show higher on-current especially in N-channel. Figure 3.19 shows the characteristic variability in TFTs in both patterns. As shown in Fig. 3.19(a), TFTs with the conventional pattern showed large variation although only a fewer numbers of TFTs could be operated. On the other hand, TFTs with the strip pattern showed high-performance and smaller variation, as shown in Fig. 3.19(b). Figures 3.20(a) and (b) show histograms of the characteristic variability of threshold voltage ( $V_{th}$ ), field effect mobility ( $\mu_{FE}$ ) and subthreshold swing value (S) of TFTs in both patterns. Characteristic variability in strip pattern was reduced to roughly 1/3, by comparison with conventional

Fig. 3.18 Transfer characteristics of TFTs fabricated with conventional (broken line) and strip pattern (solid line). Insets were optical images of TFTs with (a)conventional pattern, (b) strip pattern, and (c) agglomerated conventional pattern.

Fig. 3.19 Transfer characteristics of TFTs with (a) conventional and (b) strip pattern. No good TFTs, such as gate leakage and pattern defects, were eliminated among 35 TFTs.

Fig. 3.20 The histograms of  $V_{\text{th}}$ ,  $\mu_{\text{FE}}$ , and S in TFTs with (a) conventional and (b) strip pattern. Average  $\pm$  standard deviation ( $\sigma$ ) of NMOS and PMOS were shown, respectivery.

pattern. However, the p-ch characteristics of the strip TFTs shifted to left compared to the conventional TFTs. We concluded that the differences of p-ch TFTs were caused by small

amount of defects and un-doped channels which behaved as n-type. Thus acceptor-type defect density in strip TFTs is lower than in conventional TFTs. These results indicate that reduction of random GBs effectively suppresses the variability and improve the  $\mu_{FE}$ .

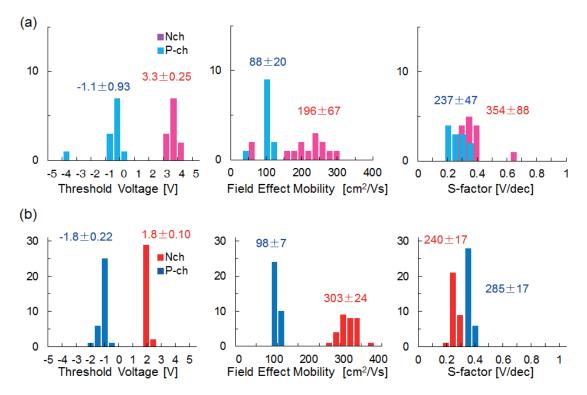

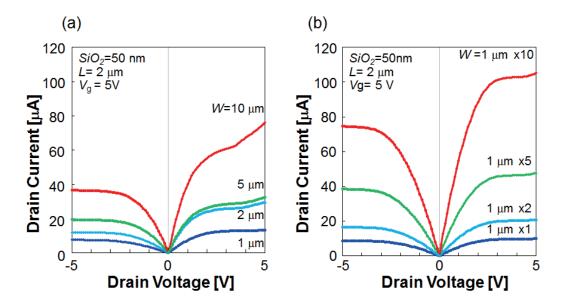

So we investigated the application of strip TFTs to CMOS operation. Figure 3.21 shows the output characteristic of TFT with strip pattern.

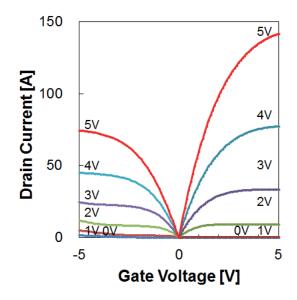

# 3.3.4 CMOS circuit operation

In order to control the output of CMOS invertor, NMOS and PMOS outputs were investigated. Figure 3.21 shows output characteristics of strip pattern TFTs. They were quite promising for the operation at supplying voltage ( $V_{dd}$ ) of 5V and the size ratio ( $R = W_P/W_N$ ) for CMOS layout was well-balanced at R = 2. As shown in Fig. 3.22, CMOS inverter with the strip pattern operated at a low supply voltage of 5 V with no hysteresis and showed a  $V_{th} = 2.5$ V at R = 2.

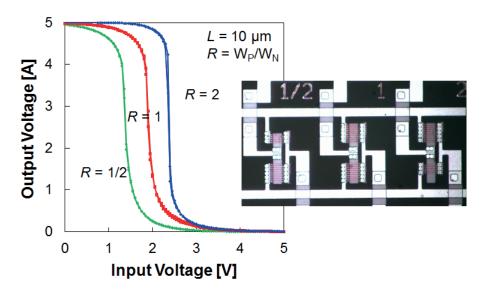

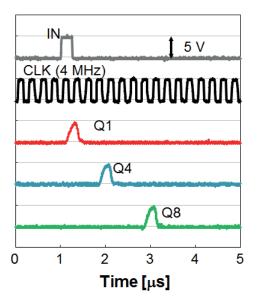

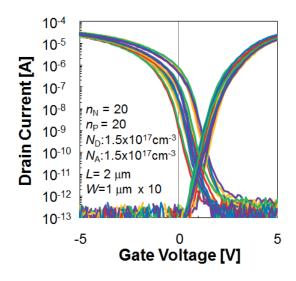

We fabricated a shift register (SR), which is a key circuit for peripheral circuit formation on glass substrate [27-30]. To evaluate the effect of channel patterns, we fabricated SR with both patterns. We could not operate SRs with conventional pattern because of the poor yield as mentioned previously. We fabricated the SR with the strip channel pattern as shown in Fig. 3.23. We were able to operate 8-bit shift-register at a supply voltage of 5V and a clock frequency of 4 MHz as shown in Fig. 3.24. This low-voltage operation was achieved because the proposed strip channel pattern can effectively to improve both the yield and performance of TFTs. This result demonstrates that the  $\mu$ -TPJ crystallization process on a-Si strip pattern is quite promising for the fabrication of high-performance displays.

Fig. 3.21 Output characteristics of TFTs with strip pattern. NMOS and PMOS were same size and evaluated by the condition with  $V_{gs}$  of 5V and  $V_{ds}$  from 0 to 5V.

Fig. 3.22 Output characteristics of CMOS inverters with different size ratio (R). Inset shows the CMOS inverters with  $L = 10 \mu m$  and R = 1/2, 1 and 2, respectively.

Fig. 3.23 The optical microscope image of shift register (SR) with strip pattern and circuit diagram of 1 bit SR. 16 TFTs with ( $L = 10 \mu$ m) are composed in 1bit SR with a bit pitch of 169  $\mu$ m.

Fig. 3.24 Output characteristics of shift register with strip pattern operated by the supply voltage of 5V at the clock frequency of 4MHz. The input signal and shifted outputs with each bits of SR were shown.

# 3.4 Summary

We fabricated a shift register (SR), which is one of the key circuits for the peripheral driver of displays. To evaluate the effect of channel patterns, we fabricated SR with both patterns. We could not operate SRs with conventional pattern because of the poor yield as mentioned previously. We fabricated the SR with the strip channel pattern. We were able to operate 8-bit shift-register at a supply voltage of 5V and a clock frequency of 4 MHz. This low-voltage operation was achieved because the proposed strip channel pattern can effectively to improve both the yield and performance of TFTs. This result demonstrates that the  $\mu$ -TPJ crystallization process on a-Si strip pattern is quite promising for the fabrication of high-performance displays.

# References

- S. Hayashi, S. Higashi, H. Murakami, and S. Miyazaki, Appl. Phys. Express 3, 061401 (2010).

- [2] M. Kimura, S. Inoue, T. Shimoda, and T. Sameshima, Jpn. J. Appl. Phys. 40, L97 (2001).

- [3] M. Kimura, Jpn. J. Appl. Phys. 50, 03CB01 (2011).

- [4] M. Kimura and A. Nakashima, Jpn. J. Appl. Phys. 51, 03CA05 (2012).

- [5] S. Hayashi, Y. Fujita, T. Kamikura, K. Sakaike, M. Akazawa, M. Ikeda, H. Hanafusa, and S. Higashi, Appl. Phys. Lett. **101**, 172111 (2012).