広大科研 19 17560309 0100454020

# 超高耐放射線・気体絶縁ゲート 電界効果トランジスタの研究

# 課題番号 17560309

平成17年度~平成18年度 科学研究費補助金 (基盤研究(C)) 研究成果報告書

平成19年5月

研究代表者 角南英夫 (広島大学ナノデバイス・システム研究センター 教授)

# 基盤研究 (C)

広大科研 19 17560309 0100454020

超高耐放射線・気体絶縁ゲート電界効果トランジスタの研究

# 研究組織

研究代表者: 角南英夫 広島大学ナノデバイス・システム研究センター教授

研究協力者: 芦田洋一、奥山清

# 交付決定額(配分額)

(金額単位:千円)

|          | 直接経費  | 間接経費 | 合計    |

|----------|-------|------|-------|

| 平成 17 年度 | 2,400 | 0    | 2,400 |

| 平成 18 年度 | 1,100 | 0    | 1,100 |

| 総計       | 3,500 | 0    | 3,500 |

# 研究発表

(1) Youichi Ashida, Kiyoshi Okuyama, and Hideo Sunami, "Influence of Forced Gate Insulation Breakdown on Transistor Performance for Newly Proposed Metal-Gas-Semiconductor Field-Effect Transistor," to be submitted to Microelectronic Engineering.

# 目 次

| 第1章 | 序論                          | 貝  |

|-----|-----------------------------|----|

| 1.1 | 本研究の背景                      | 1  |

| 1.2 | 本研究の目的                      | 3  |

| 1.3 | これまでの研究経過と斯界の動向             | 4  |

| 1.4 | 研究成果とその展開                   | 4  |

| 第2章 | MGS トランジスタの試作               |    |

| 2.1 | 試作プロセス工程                    | 11 |

| 2.2 | 試作個別プロセス                    | 17 |

| 第3章 | 試作した TEG パターンと完成したウェハ       |    |

| 3.1 | TEG パターン                    | 29 |

| 3.2 | 試作したウェハとチップの外観              | 31 |

| 第4章 | トランジスタの電気特性評価               |    |

| 4.1 | 実効チャネル長の算定                  | 33 |

| 4.2 | Id-Vd 特性および Id-Vg 特性 ······ | 34 |

| 4.3 | 電流駆動能力                      | 37 |

| 4.4 | 最大トランスコンダクタンス               | 38 |

| 4.5 | サブスレッショルド係数                 | 40 |

| 4.6 | しきい電圧                       | 43 |

| 第5章 | 強制破壞試験結果                    |    |

|     |                             |    |

| 5.1 | 測定回路                        | 45 |

| 5.2 | ゲート絶縁強制破壊試験                 | 46 |

| 5.3 | ゲート絶縁強制破壊後のトランジスタ特性         | 51 |

| 5.4 | 最大トランスコンダクタンス               | 55 |

| 第6章 | 強制破壊試験結果               |    |

|-----|------------------------|----|

| 6.1 | MGS トランジスタのゲート耐圧破壊後の特性 | 57 |

| 6.2 | トランジスタの不揮発性メモリ効果       | 60 |

| 第7章 | 結論                     |    |

| 7.1 | 研究結果のまとめ               | 61 |

| 7.2 | 今後に残された課題              | 61 |

| 謝辞  |                        | 61 |

#### 第1章 序論

# 1.1 本研究の背景

1970年以来、シリコンのLSI(Large Scale Integration: 大規模集積回路)の高速化および大規模化は共に10年で100倍の割合で向上しており、今後も同じ割合を保ち続けることが期待されている。それは、今日の情報・通信産業が車の両輪としてハードウェアとソフトウェアの性能向上によって支えられており、かつハードウェアの進展は主に集積回路の性能向上に依存してるからに他ならない。

LSI の性能向上には、トランジスタなど集積する素子の微細化が最も寄与している。これは、トランジスタの寸法を一定のルールで縮小化すると、スケーリング則  $^{11}$  に従って動作速度や消費電力などの性能が向上するというものである。また、トランジスタの寸法を小さくすることによりウエハ1 枚あたりの集積回路チップの収量が増えるためコストを下げることができる。これらの利点から集積回路のトランジスタが縮小化されてきた。1970年には  $12\mu m$ 、その後 3 年毎に 0.7 倍に縮小され、その結果、現在研究レベルではゲート長 15nm の極微細トランジスタが試作されている  $^{21}$ 。 30 年間にほぼ 1/1000 の大きさに縮小された。

現在での LSI はほとんどすべてが MOS(metal-oxide-semiconductor:金属 – 酸化膜 – 半導体) 型であるから、その構造とプロセスのトレンドを図 1.1 に示す  $^3$  。結果としてこの表に記したようなトレンドを実現してきた。

|          | 19                    |               |          | 1980    |        |                                         | 1990<br><u></u> |              |           | 201      |        |       |      |       |  |

|----------|-----------------------|---------------|----------|---------|--------|-----------------------------------------|-----------------|--------------|-----------|----------|--------|-------|------|-------|--|

| 技術       | トラフード (μ <b>m</b> )   | 12            | 8        | 5       | 3      | 2                                       | 1.3             | 0.8          | 0.5       | 0.3      | 0. 2   | 0.13  | 0.09 | 0.065 |  |

| DRA      | (M容量 (ビット)            | 1K            | 4K       | 16K     | 64K    | 256K                                    | 1M              | 4M           | 16M       | 64M      | 256M   | 1G    | 4G   | 16G   |  |

| DRAM     | 構造                    | 3Tr.          |          |         | 1Tr,プレ | ノーナ                                     |                 |              | スタ        | ック o     | r トレン  | チ     |      | 新セル?  |  |

| セル       | 等価絶縁膜厚<br>(nm)        | 120           | 100      | 50      | 35     | 20                                      | 10              | 8            | 5         | 4        | 3      | 2     | 1    | 0.5   |  |

| _,,      | 電源電圧 (V)              | 20            | 1        | 2       |        | ·                                       | 5               |              | 内部3.3     | 3        | . 3    | 2.5   | 1.   | .5    |  |

|          | トランジスタ                | pMOS          |          | nMOS    |        |                                         |                 |              |           | MOS      |        |       | 次元   |       |  |

| デバ       | ドレイン構造                |               | 単一ドレイン   |         |        | 二重ドレイン                                  |                 |              | LDD HDD   |          |        | 伸張    | ハロー  | — SOI |  |

| イス       | 酸化膜厚(nm)              | 120           | 100      | 75      | 50     | 35                                      | 25              | 20           | 15        | 12       | 8      | 5     | 3    | 2     |  |

|          | チャネル長(μm)             | 8             | 5        | 3       | 2      | 1.3                                     | 0.8             | 0.8          | 0.5       | 0.3      | 0.2    | 0.13  | 0.09 | 0.065 |  |

|          | 接合深さ (μm)             | 1.5           | 0.8      | 0.5     | 0.35   | 0.3                                     | 0.25            | 0.2          | 0.15      | 0.12     | 0.1    | 0.08  | 0.05 | 0.03  |  |

|          | リソグラフィ                |               | コンタク     | ト 1/1投影 |        | 1/10<br>ステッパ 1/5ステ                      |                 | ッパ (g線) (i線) |           | ) KrF スキ |        | ・ャナ   | ArF  | ArF液浸 |  |

| <b>-</b> | エッチング                 |               | 溶液       |         |        |                                         | プラズマ, RIE       |              | ECR       |          | R HDP  |       | ICP  |       |  |

| プロ       | 素子分離                  | プレー           | <b>+</b> | LOC     | OS     | **************************************  | 改良LOCOS         |              |           | リセス      | 11 200 | 浅溝    | 深溝   |       |  |

| セス       | ゲート材料                 | - ト材料 AI ポリSi |          | 二層7     | 二層ポリSi |                                         | ポリサイド           |              | <b>イド</b> |          | ์ Wポリ  | lSi : | シリサイ | ド金属   |  |

|          | 配線金属                  | Al            |          |         | Al-Si  | THE PERSON NAMED IN THE PERSON NAMED IN | Al-Si-Cu (TiW   |              |           | W,TiN) W |        |       |      |       |  |

|          | ウエハ(mm <sup>φ</sup> ) | 50            | 60       | 75      | 100    | 125                                     |                 | 150          |           | 200      |        | 300   |      | 450   |  |

図 1.1 MOS-LSI プロセス・デバイスのトレンド

トランジスタが微細化されると、様々な部分の耐圧が低下する。ソースとドレインの距離(チャネル長)が短くなると、ソースとドレイン間の耐圧が低下する、ゲート酸化膜が薄くなると絶縁耐圧も低下する。酸化膜の絶対的な耐圧はほぼ  $10^5 \text{V/m}$  であるから、90nm 時代に要請される 1nm 厚の絶縁膜には 1V も印加できない。

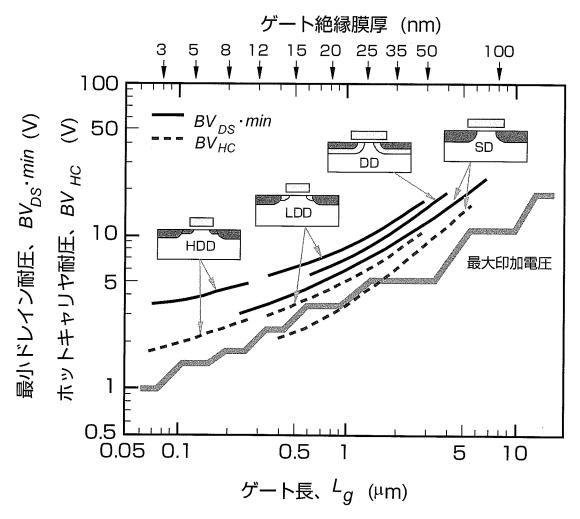

そのため MOS トランジスタ構造は改良されてきた。その一部を図 1.2 に示す  $^3$ 。ソースとドレイン間の耐圧は最小ドレイン耐圧、 $BV_{DS}$ ・min で表し、ホットキャリヤ耐圧は  $BV_{HC}$  で表わす。ほっとキャリヤとは、ソース - ドレイン間に流れる電流電子のエネルギーが大きくなると、エネルギーの大きな電子が発生し、これが  $SiO_2$  膜 - Si 基板界面のエネルギー障壁の高さ、約 2V を超えて膜に侵入し、トランジスタ特性を劣化するものである。  $BV_{HC}$  は経験的に  $BV_{DS}$ ・min より、1-2 V 低い電圧で現れる。

これらの MOS トランジスタの耐圧を挙げるために、いいかえればチャネル長が縮小されても極力、各種の耐圧の劣化を抑制するために新しい構造が導入されてきた。これらは皆、ドレイン端の電界強度を弱める目的を持っている。ただ、HDD は低濃度トレインLDD の低駆動能力を高めるために導入されたものである。

図 1.2 MOS トランジスタの最小ソース – ドレイン間耐圧 : $BV_{DS}$ : min、およびホットキャリヤ耐圧 : $BV_{HC}$ の変遷。

SD:single drain(単ドレイン), DD:double drain(二重ドレイン), LDD:lightly-doped drain(低濃度ドレイン), HDD:highly-doped drain(高濃度ドレイン).

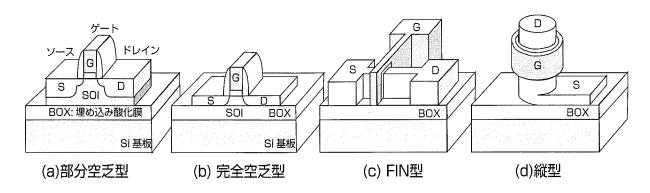

このような平面トランジスタの微細化が困難になると、図 1.3 に示すような SOI (silicon-on-insulator: 絶縁膜上シリコン) を用いた薄膜シリコントランジスタやシリコン 梁状トランジスタ  $^{48}$ 、FINFET  $^9$  などが開発され、さらには垂直方向に電流を流す 柱状トランジスタも開発されつつある。

図 1.3 開発中の各種トランジスタ ((a) → (d) の順に実現時期が遅いと推定される)

### 1.2 本研究の目的

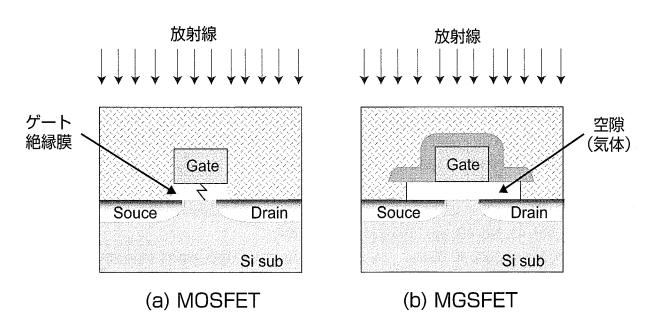

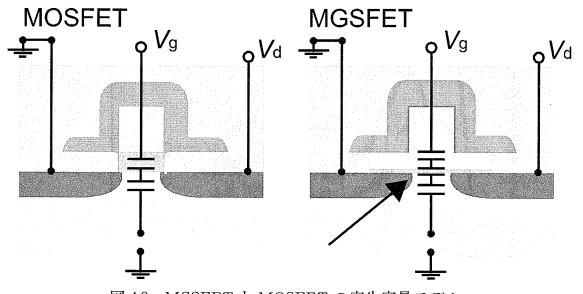

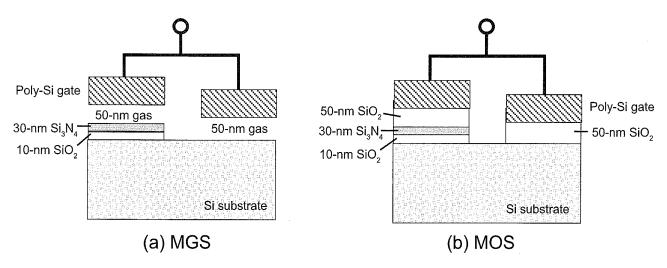

また、これらの様々な耐圧低下の現象と共に、MOSトランジスタはごく薄い絶縁膜のため、放射線や宇宙線の障害を受けやすい。このような MOSトランジスタの欠点を抜本的に解決すべく、本研究では図1.4に示すような、MOSトランジスタの酸化膜が気体のトランジスタを提案し、その試作結果を報告するものである。これを金属 – 気体 – 半導体 MGS(metal-gas-semiconductor)トランジスタをと命名した。

図 1.4 本研究で提案し、試作・評価した金属 – 気体 – 半導体 MGSFET (metal-gassemiconductor field-effect transistor)。ゲート直下が空隙(気体)となっている。放射線で障害をうける絶縁膜がない。

#### 1.3 これまでの研究経過と斯界の動向

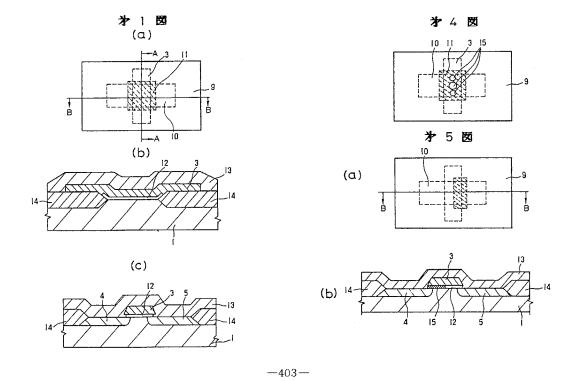

筆者の知りうる限りこれと同じ構造を試作し評価した発表はない。ただ、筆者は 1980 年代から MOS トランジスタの絶縁膜の課題を強く認識しており、1985 年に図 1.5(1)-(6) に示す特許を出願している。

#### 1.4 研究成果とその展開

第2章以降に述べるが、本MGSトランジスタは対放射線では高い耐圧を有する可能性はあるが、現時点ではまだトランジスタの形成では最適化されておらず、ゲートを強制的に破壊した後にはトランジスタそのものも破壊されており、目的が達成できていない。今後の課題である。

# <参考文献>

- 1) R. H. Dennard, F.H.Gaensslen, H-N. Yu, L. Rideout, E. Bassous, and A. R. LeBlanc, IEEE J.Solid-State Circuits, SC-9, 256, 1998.

- 2) B. Yu, H. Wang, A. Joshi, Q. Xiang. E. Ibok, and M-R. Lin, "15nm Gate Length Planar CMOS Transistor," IEDM Technical Digest, 2001.

- 3) 角南英夫,「VLSI工学 製造プロセス編 」,電子情報通信学会編,コロナ社,2006 年8月。

- 4) D. Hisamoto, W-C. Lee, et.al., "A Folded-Channel MOSFET for Deep-sub-tenth Micron Era," IEDM Tech. Digest, pp. 1032-1034,1998.

- 5) T. Furukawa, H. Yamashita, and H. Sunami, "A Proposal of Corrugated-Channel Transistor (CCT) with Vertically-Formed Channels for Area-Conscious Applications," Jpn. J. Appl. Phys., Vol. 42, Part 1, No. 4B, pp. 2067-2072, April 2003.

- 6) H. Sunami, T. Furukawa, and T. Masuda, "A Three-Dimensional MOS Transistor Formation Technique with Crystallographic Orientation-Dependent TMAH Etchant," SENSORS and ACTUATORS A: PHYSICAL, A111, pp. 310-316, 2004.

- A. Katakami, K. Kobayashi, and H. Sunami, "A High-Aspect Ratio Silicon Gate Formation Technique for Beam-Channel MOS Transistor with Impurity-Enhanced Oxidation," Jpn. J. Appl. Phys., Vol. 43, No. 4B, pp. 2145-2150, April 2004.

- 8) H. Sunami S. Matsumura, K. Yoshikawa, and K. Okuyama, "High-aspect-ratio structure formation techniques for three-dimensional metal-oxide-semiconductor transistors," Microelectronic Engineering, Vol. 83, pp. 1740-1744, March 2006.

- 9) Y-K. Choi, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Anderson, T-J. King, J. Bokor, and C. Hu, "Sub20nm CMOS FinFET Technologies," IEDM Tech. Digest, pp. 421-424, 2001.

(9) 日本国特許庁(JP)

⑪特許出願公開

# ⑩ 公 開 特 許 公 報 (A) 昭61 - 183969

⑤Int,Cl.<sup>4</sup> 識別記号

H 01 L 29/78 21/28 29/60

8422-5F 7638-5F

29/60 // H 01 L 27/08 ....

6655-5F 審査請求 未請求 発明の数 1 (全6頁)

❷発明の名称 電界効果トランジスタ

②特 願 昭60-23085

102

②出 願 昭60(1985) 2月8日

⑩発 明 者 角 南 英

夫 国分寺市東恋ケ窪1丁目280番地 株式会社日立製作所中

央研究所内

⑪出 願 人 株式会社日立製作所

東京都千代田区神田駿河台4丁目6番地

⑭代 理 人 弁理士 中村 純之助

#### 明細書

1. 発明の名称 電界効果トランジスタ

#### 2. 特許請求の範囲

基板上に形成したソースおよびドレインと、該ソースおよびドレイン間のチャネル上に該ソースおよびドレインと電気的に分離されたゲートとを具備する電界効果トランジスタにおいて、上記ゲートと上記チャネルとの間の一部もしくは全部が10<sup>-1°</sup> Pa以上の圧力の気体で満たされていることを特徴とする絶縁ゲート形電界効果トランジスタ。3.発明の詳細な説明

#### [発明の利用分野]

本発明は絶縁ゲート形電界効果トランジスタに 関する。

#### 〔発明の背景〕

MCS形トランジスタを微小化すると、キャリヤとしての電子に対する電界が強くなって、高いエネルギーを持つ、いわゆる有害なホットエレクトロンが増大する。このホットエレクトロンにつ

いては、日経エレクトロニクス1979年9月17日号 74頁~87頁に詳述されている。

このホットエレクトロン現象は半導体デバイス の物理に根ざしたものであり抜本的に解決することは困難と見られていた。

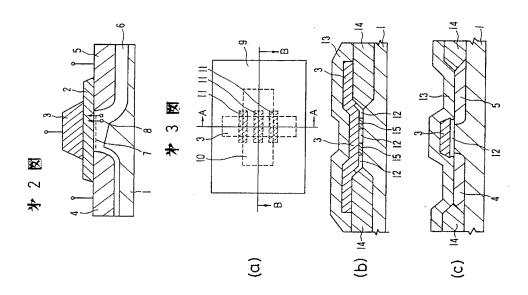

第2回にnチャネルIGFET (絶縁ゲート形電界効果トランジスタ) の断面図を示す。

図において、1はp形Si基板、4、5はそれぞれp形Si基板1の表面部に形成されたn形のソースとドレイン、7はソース4とドレイン5との間のチャネル、2はp形Si基板1の表面上に形成されたSiO $_2$ で代表される絶縁膜、3は絶縁膜2上に形成された9結晶Siで代表されるゲートである。

このトランジスタに電圧をかけると、ソース 4 から流れ出たキャリヤ (エレクトロン) がチャネル7を通ってドレイン 5 に到達し、チャネル7、ソース 4、ドレイン 5 は空乏層 6 で包まれる。

ホットエレクトロン8は、チャネル7中を流れるキャリヤがドレイン5に印加したドレイン電圧

-399-

図 1.5 (1) 出願特許(特願昭 60-23085 )明細書の1頁。

#### 特開昭61-183969(2)

Vpoによって加速され、Si 基板1の格子と衝突 して作られる。

このホットエレクトロン8はSi〇₂の絶縁膜2とSi族収1の界面の電気的バリヤ(約3eV)を越えて絶縁膜2中のトラップに捕えられる。するとトランジスタのしきい電圧VTHが捕えられたエレクトロンの量に応じて正の方向に増大したり、トランジスタの相互コンダクタンスgmが劣化したりする。

これが原因となって、このトランジスタを用いた 集積回路の動作速度が遅くなったり、最終的には動作しなることが起きる。

#### (発明の目的)

本発明の目的は、このホットエレクトロン現象 が発生しても絶縁ゲート形電界効果トランジスタ の特性が劣化しない構造を提供することにある。 [発明の概要]

本発明は、ホットエレクトロンが発生してチャネルから絶縁膜に飛び込んでもトラップに捕えられない構造を有する。

上の圧力の例えばHeやArなどの気体で満たされている。

次に、上記第1の実施例のIGFETの製造方法について述べる。

まず、p形Si基板1上に、よく知られたLOCOS法によって厚さ100nmのSiO。からなるフィールド酸化膜14を被着してフィールド領域9を形成する。フィールド領域9以外の部分は後にトランジスタを形成する活性領域10である。

この後、チャネル7とすべき領域上に、後に除去する厚さ10nmのSi,N,からなる除去膜11 (第1図 (a) の一点鎖線で示す)を被着する。

次に、Si,Na膜11およびフィールド酸化膜14 上に、厚さ300nmの多結晶 Siからなるゲート 3 を被着する。

その後、Si,N,MI1を、100℃以上に昇温したリン酸の液の中に没して除去すると、ゲート3は除去されず残るので、第1図(b)のAA斯面図に示すようにゲート絶縁領域12は空洞となる。

この後、リンあるいはヒ素をそれぞれ5×10<sup>15</sup>

一般に、絶縁限は多少なりともトラップを有するので、本発明においては、ゲートとチャネルとの間の一部もしくは全部を、トラップの全くない低真空もしくは圧力10<sup>-1°</sup> Pa(現在地球上で得られる最低の圧力)以上の圧力の気体を満たすことによって、トラップを全く生じさせず、あるいは減少させてホットエレクトロン現象に起因するトランジスタの特性の劣化を防止するものである。

第1回 (a) は本発明の第1の実施例のn チャネルIGFETの平面図、第1図 (b) は第1図 (a) のAA斯面図、第1図 (c) は第1図 (a) のBB斯面図である。

図において、1 は p 形 S i 基板、4、5 はそれぞれ p 形 S i 基板 1 の表面部に形成された n 形のソースとドレイン、7 はソース4 とドレイン 5 との間のチャネル、3 は多結晶 S i からなるゲート、13 は 層間 絶 糅膜、14 はフィールド酸 化膜、9 はフィールド領域、10 は活性領域、12 はゲート 3 とチャネル7 との間のゲート絶縁領域で、10<sup>-10</sup> P a 以

cm - \* イオン打込みし、ソース4、ドレイン5を形成する。

及後に、CVD法によりPSG(リンガラス)からなる厚さ500nmの層間絶縁膜13を形成する。ゲート絶縁領域12の空洞は、層間絶縁膜13の形成により周囲がすべて包囲され、かつCVD・PSGからなる層間絶縁膜13を形成する時に発生するガスで満される。本実施例では、上記CVD法において、SiH・とPH。の熱分解法を用いたので、ゲート絶縁領域12がH。が主成分である形成ガスで充填された。

なお、本実施例では除去膜11として $Si_s$   $N_s$  膜を用いたが、原理的には除去膜11を除去するときにフィールド酸化膜14やゲート3を有害なほどエッチングしなければよいので、他の膜、たとえばWやMoなどのリフラクトリーメタル、 $Ta_zO_s$ 等の膜を用いることができる。

なお、 W、 Mo、 Ta<sub>2</sub> O<sub>5</sub> はそれぞれ濃過酸化水 素水、硝酸: フッ酸: 水酢酸: 水 (75:15:5: 5) の混液、フッ酸のバッファ液で除去すること

-400-

図 1.5 (2) 出願特許 (特願昭 60-23085) 明細書の 2 頁。

#### 特開昭61~183969(3)

ができる。

ところで、Siは湿気のある空気中に放置することで厚さ 2 nm 厚前後の自然酸化膜が形成されるので、実際には、ゲート絶縁領域12下のSi 基板1 表面および、ゲート絶縁領域12上の多結晶 Si ゲート 3 下面には厚さ 2 ~ 3 nm の Si O 2 膜が形成されている場合がある。

また、本実施例では、ゲート3上に被着する膜としてCVD法によるPSG膜13を用いた。この 層間絶縁膜としては、MOSトランジスタに悪影響を及ぼさない膜であれば原理的には何でもよい。 のえばSiO。やSi,N。膜は、スパッタ法によって0.2~0.5 Paの低真空下のArガスを用いて堆積することができる。この場合空洞となるゲート絶縁領域12は同上の圧力のArで満たされる。Arは不活性ガスであり、化学的反応性は非常に低いので、トランジスタの特性上望ましい。スパッタ法においては、よくArが用いられるが、XeやNe、He等も同様に用いることができる。さらに、層間終縁膜13の堆積法としてCVD法とスパッタ法

に示す如く、厚さ10nmのSi,N,からなる除去膜 11を編状に形成する。

除去膜11を形成した後、チャネル7となるべき部分のSi基板を酸化して除去膜のない部分に厚さ10nmのSiO2からなるゲート酸化膜15 (スペーサ)を形成する。

その後、上記第1の実施例と同様にしてゲート3を形成し、除去膜11を除去すると、第3図(a)~(c)に示すようなゲート絶糅領域12の空洞内にスペーサとしてゲート酸化膜15を設けた本発明の第2の実施例を得ることができる。

本実施例の場合、ゲート絶縁領域12内にゲート酸化膜15が存在するので、このゲート酸化膜15の部分においてはホットエレクトロンがトラップに捕えられて特性が変化するが、ゲート酸化膜15の領域を極力小さくすることで実質的な影響がないようにすればよい。

また、上記第2の実施例では、第3図(a)に示したように、チャネル長方向(ソース・ドレインを結ぶ方向)に縞状をなしているが、チャネル

の他、真空蒸煮法なども用いることができる。

さらに、上記の堆積法を一種だけ用いて層間絶 縁膜13を形成するばかりでなく、初期においては スパッタ法で被着し、途中からCVD法に替えて 断たな層間絶縁膜13を積層するいわゆる多層積層 膜を用いることもできる。すなわち、CVD法は 下地の凹凸のある段差にカバレジよく被着できる ので、信頼性の高い集積回路が形成できる。

第3図(a) は本発明の第2の実施例のn チャネルIGFETの平面図、第3図(b) は第3図(a) のA A 断面図、第3図(c) は第3図(a) のB B 断面図である。

上記の第1の実施例においては、ゲート絶縁領域12をすべて空洞としたが、チャネル7の領域が広い場合は、ゲート3とSi基板1表面のチャネル7との距離が不均一となったり、接触したりすることが起るので、スペーサを設けてもよい。本実施例は、ゲート絶縁領域12の空洞内にスペーサを設けた例を示す。

すなわち、本実施例においては、第3図 (a)

幅方向に 額状をなしてもよい。 なお、第4回に示すように、三つの孔を形成した除去膜11を用いることにより、三つの柱状のゲート絶縁膜15を形成することができる。この本発明の第3の実施例では、ゲート絶縁領域内に占めるゲート絶縁膜15の割合が小さいので、トランジスタの劣化の度合もまた小さくすることができる。

一方、ホットエレクトロンは、主にドレイン5に近い部分で発生するので(第2回参照)、ドレイン5に近い部分のゲートSiO。膜を除去すれば、本発明の効果を達成することができる。このような構造を有する本発明の第4の実施例の平面図を第5図(a)に示す。また、第5図(b)は第5図(a)のBB斯面図である。

すなわち、本実施例では、第5図(a)に示す如く、ドレイン5に近い部分だけに除去膜!!を設けた。

本実施例の場合は、ソース4に近い部分に SiOz膜15を設けたので、ゲート絶縁膜の誘電率 εに比例するトランジスタの相互コンダクタンス

**-401-**

図 1.5 (3) 出願特許(特願昭 60-23085) 明細書の 3 頁。

#### 特開昭61~183969 (4)

gmの低下を抑えることができる。その理由は、SiO.からなるゲート絶縁膜の誘電率は、真空や1気圧程度の気体の約3.9倍である。すなわち、第1図(a)~(c)で示した第1の実施例のように、チャネル7上のゲート絶縁領域12がすべて気体で満たされていると、トランジスタの相互コンダクタンスgmは、SiO.膜からなるゲート絶縁隙の場合より約1/3.9に低下する。

また、前に述べたように、気体を満たしたゲート総縁領域12下のチャネル7のSi基板1の表面は厚さ2nm前後の自然酸化膜が存在する場合があると述べたが、この部分のSi基板1の表面に意図してゲート絶縁膜を形成することもできる。この場合には、トランジスタのゲート絶縁領域は、気体とこのゲート絶縁膜の二層構造になるので、総合の誘電率はゲート絶縁膜の厚さと誘電率に応じて増大し、相互コンダクタンスgmの向上に効果がある。

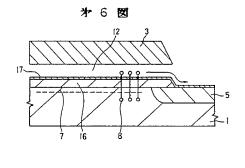

また、第6回に示すように、本発明によるトランジスタでは、チャネル7からホットエレクトロ

ルトランジスタにおいては正孔は衝突電離を起し にくいためホットエレクトロン現象が起きにくい ので、nチャネルトランジスタにおける程、信頼 性の問題が顕著でない。 また、本発明を用いて 同一Si基板上にnチャネルトランジスタとpチャネルトランジスタを形成したCMOS回路を構 成することができる。pチャネルを形成するとき は n チャネル側をホトレジスト等で覆っておき、 n チャネルを形成するときは逆にpチャネル側を ホトレジスト等で覆っておけばよい。

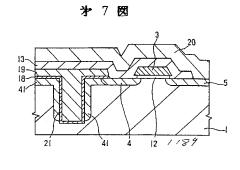

本発明の第6の実施例を第7図に示す。

すなわち、p形Si 基板1上に深さ4皿の溝21をドライエッチング法により形成し、外壁にSbのガス拡散を用いてn\*層のソース41を形成する。

その後、再び神21を 1 m 程度深くエッチングすると、第 7 図に示すようにソース41が左右に分離できる。

この後、SiOzやSizN.の単層あるいはそれらの多層膜を厚さ20nn被着してキャパシタ絶縁膜18を被着する。

ン8がゲート絶縁領域12に飛び込み、ゲート3に 電流として流れるが、そのホットエレクトロン8 の一部は、チャネル7上の自然酸化膜もしくは意 図して形成したゲート絶縁膜16の表面上に残る可能性がある。

ところで、この絶縁膜16上に残存するホットエレクトロンは、絶縁膜16の表面に、第6図に示す如く、導電膜17を形成して導電性を持たせ、この 導電膜17をドレイン5に接続しておけば絶縁膜16 表面上に留まることなくドレイン5に流れ込む。

ただし、導電膜17の導電率が余り大であると、 ゲート3がドレイン5によって電気的に遮蔽され てしまうので、ホットエレクトロンが十分流れる 程度の小さい導電率をもたせ、トランジスタ動作 を損なわないようにする。

以上説明した本発明の第1~第5の実施例においては、nチャネルトランジスタを用いたが、pチャネルトランジスタにも適用してもよい。その場合には、すべての不純物をp形からn形へ、n形からp形へ変換すればよい。ただし、pチャネ

次いで、厚さ0.3μmの多結晶Siで代表されるプレート19を被着して溝21を埋める。

この後は、第1~第5の実施例で述べた本発明のトランジスタを形成し、厚さ1㎞のA&で代表されるビット線20を形成すれば、滯の個壁をキャパシタとする1トランジスタ形ダイナミックメモリを形成することができる。

ダイナミックMOSメモリはLSIの中でも最も微細化されており、トランジスタも小さい。従って、ホットエレクトロンの影響をうけやすいので本発明の適用は特に効果がある。

「発明の効果」

本発明によれば、ホットエレクトロン現象によるトランジスタ特性の劣化を防止することができるので、信頼性の高い集積回路を構成できるだけでなく、特に微細なトランジスタの信頼性を高めるのに好適である。

4 - 図面の簡単な説明

第1回(a) は本発明の第1の実施例のnチャネルIGFETの平面図、第1図(b) は第1図

<del>-402-</del>

図 1.5 (4) 出願特許 (特願昭 60-23085) 明細書の 4 頁。

#### 特開昭61-183969 (5)

(a) の A A 斯面図、第 1 図 (c) は第 1 図 (a) の B B 斯面図、第 2 図は従来の n チャネル I G F E T の 斯面図、第 3 図 (a) は本発明の第 2 の実施例の n チャネル I G F E T の 平面図、第 3 図 (c) は第 3 図 (a) の A A 斯面図、第 3 図 (c) は第 3 図 (a) の B B 斯面図、第 4 図は本発明の第 5 図 (a) の B B 斯面図、第 4 図は本発明の第 5 図 (a) は本発明の第 4 の実施例の n チャネル I G F E T の 平面図、第 5 図 (b) は第 5 図 ル I G F E T の 平面図、第 6 図は本発明の第 5 の実施例の n チャネル I G F E T の 断面図、第 7 図は本発明の第 6 の実施例の 1 トランジスタ形ダイナ まックメモリの断面図である。

1 ··· p 形 S i 基板 2 ··· ゲート絶縁膜

3 … ゲート 4 … ソース5 … ドレイン 6 … 空乏層

7…チャネル 8…ホットエレクトロン

9 … フィールド領域

10 … 活性領域

11 … 除去膜

12 … ゲート絶縁領域

13 … 層間絶縁膜

14 … フィールド酸化膜

15…ゲート酸化膜

16…チャネル領域上絶縁膜

19…プレート20…ビット線21…游41…ソース

代理人弁理士 中村 純之助

図 1.5 (5) 出願特許(特願昭 60-23085 )明細書の 5 頁。

# 特開昭61-183969 (6)

-404-

図 1.5 (1) 出願特許(特願昭 60-23085 )明細書の 1 頁。

#### 第2章 MGS トランジスタの試作

本章では、ゲート絶縁膜に従来の $SiO_2$ ではなく空隙を形成することにより、耐放射線性能向上を目的とした MGSFET の試作プロセスを記述する。プロセス手順、設定条件、TED(test element group) マスクを説明する。

# 2.1 試作プロセス工程

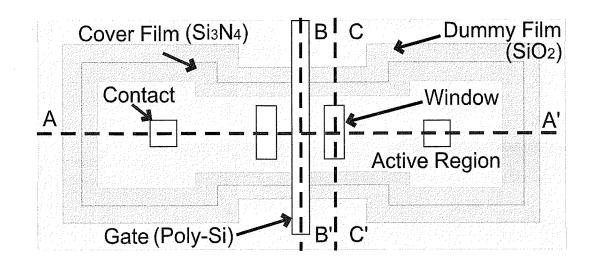

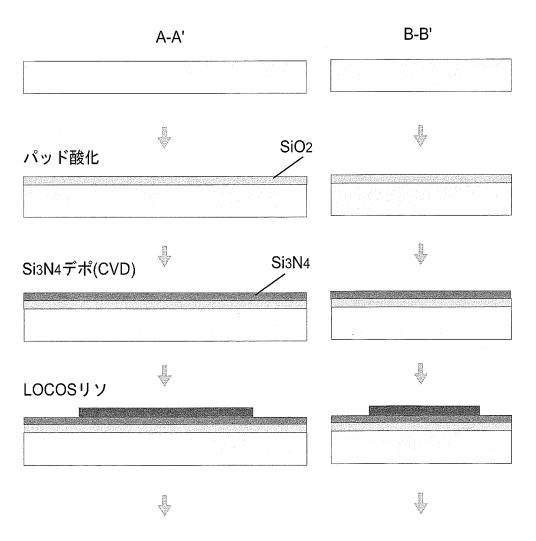

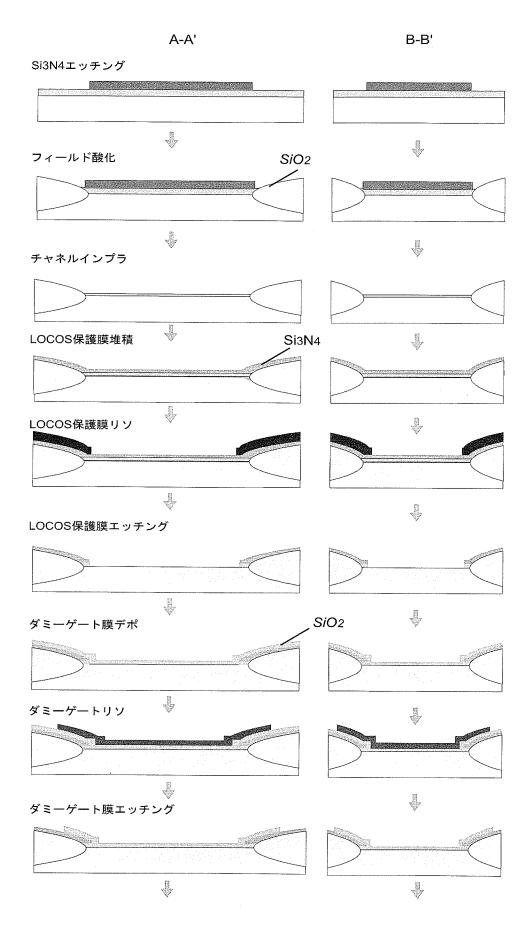

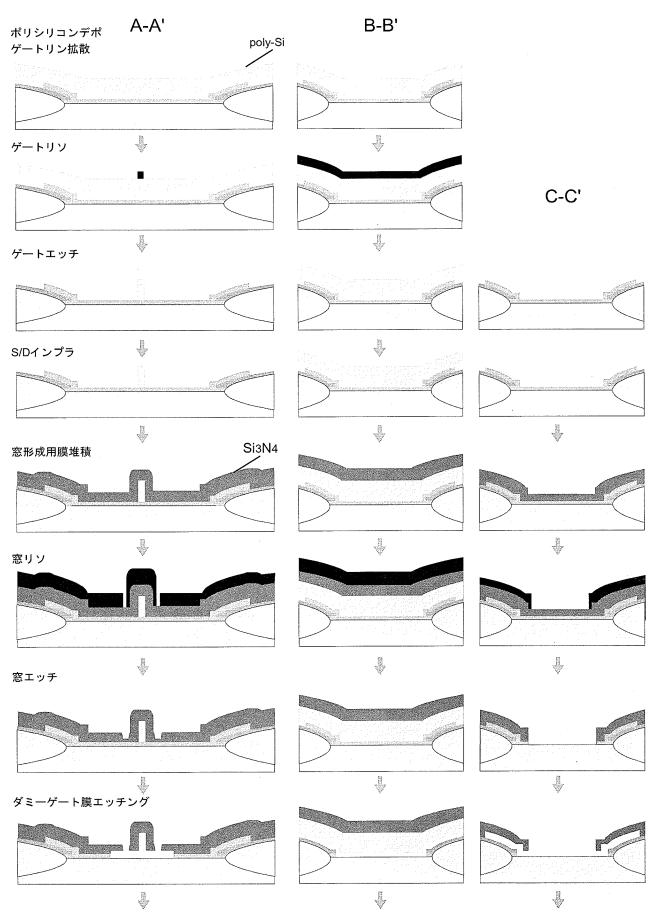

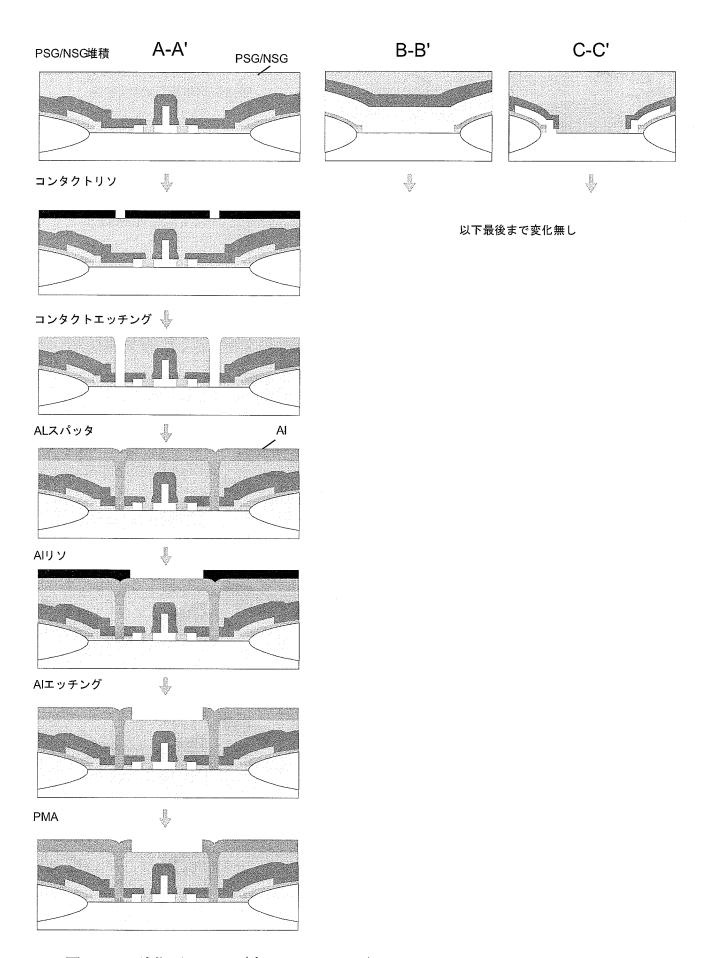

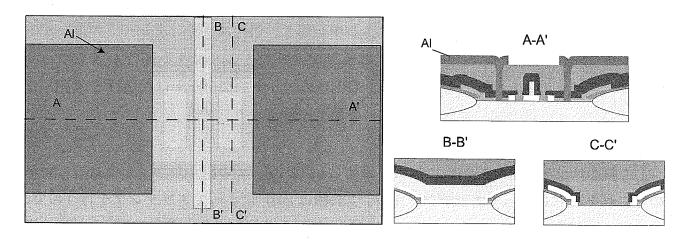

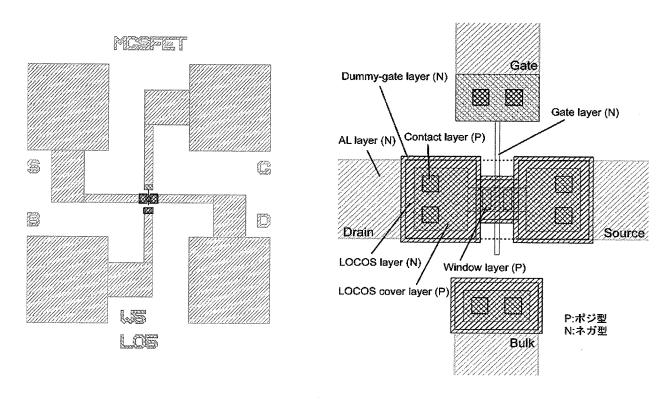

試作プロセスの一覧を表 2.1 に示す。また、図 2.1 に試作トランジスタの平面図を示し、図 2.2 に試作プロセスをトランジスタ断面図を用いて説明する。なお、トランジスタを試作したウェハ上には、工程 (8) を施さないで、ダミーゲート膜を除去しない通常の MOSトランジスタも MGSトランジスタとの特性比較をするために形成した。

## 表 2.1 試作プロセス

- (1) EB 合わせマーク形成 (装置: HL700D)

- ・EB マーク用酸化膜形成

- ・EBリソグラフィ

- ・マーク形成エッチング

1000℃ Wet ポジレジスト/ HL700D

RIE

- (2) LOCOS フィールド酸化膜形成

- ・パッド酸化膜形成

- ・Si<sub>3</sub>N<sub>4</sub> 膜堆積

- ・LOCOS リソグラフィ

- ・Si<sub>3</sub>N<sub>4</sub> 膜エッチング

- ・フィールド酸化

乾燥酸化、850℃、 30nm LPCVD、750℃、120nm ネガレジスト/ HL700D CDE

湿式酸化、1000℃、450nm

- (3) チャネル・イオン注入

- B<sup>+</sup>, 110 keV,  $5 \times 10^{12} / \text{cm}^2$

- BF<sup>2+</sup>, 140keV, 1e<sup>13</sup>/cm<sup>2</sup>

- BF<sup>2+</sup>, 30keV, 3e<sup>12</sup>/cm<sup>2</sup>

- (4) フィールド酸化膜端保護膜形成

(後の工程で行うゲートに空洞を作製するプロセス(ダミーゲート膜除去工程)において、ダミー膜に  $SiO_2$  を、そのエッチング液としてバッファー HF 溶液を採用したため、その際にフィールド酸化膜端が削られないよう に保護するための膜形成プロセス( $Si_3N_4$  膜を採用)

- ・Si<sub>3</sub>N<sub>4</sub> 膜堆積

- ・リソグラフィ

- ・Si<sub>3</sub>N<sub>4</sub> 膜エッチング

LPCVD、750℃、30nm ポジレジスト/HL700D

CDE

## (5) ダミーゲート膜形成

(ゲート部の間隙を形成するために必要な、後に除去される膜形成プロセス。本試作においては、その膜に $SiO_2$ 、エッチング液にバッファーHF液を使用)

· HTO 膜堆積

・リソグラフィ

・エッチング

LPCVD、750℃、50nm ネガレジスト/ HL700D

RIE

### (6) ゲート形成

・ポリSi 膜堆積

· P (リン) 拡散

·HTO膜(SiO2)形成

・ゲートリソグラフィ

・HTO 膜エッチング

・ポリ Si 膜エッチング

LPCVD、635℃、200nm

POCl₃炉、850℃

LPCVD、750℃、50nm

ネガレジスト/ HL700D

RIE ECR

# (7) ソース・ドレイン (S/D) イオン注入

• As, 50 kev,  $5 \times 10^{15} / \text{cm}^2$

# (8) 空隙形成

(ダミーゲート膜を除去することによってに空隙を作製するプロセス)

·Si<sub>3</sub>N<sub>4</sub> 膜堆積

・エッチング窓リソグラフィ

・Si<sub>3</sub>N<sub>4</sub> 膜エッチング

・ダミーゲート膜エッチング

LPCVD、750℃、80nm ポジレジスト/HL700D

RIE

バッファー HF 溶液

#### (9) エッチング窓充填

· NSG+PSG Deposition

APCVD,  $400^{\circ}$ C, 700nm

#### (10) コンタクト孔形成

・リソグラフィ

・エッチング

ポジレジスト/ HL700D

RIE + バッファー HF 溶液

# (11) Al 電極形成

・Alスパッタ

・リソグラフィ

・Alエッチング

#### 600nm

ネガレジスト/ HL700D

溶液

#### (12) PMA

・H2アニール

400°C、30nm

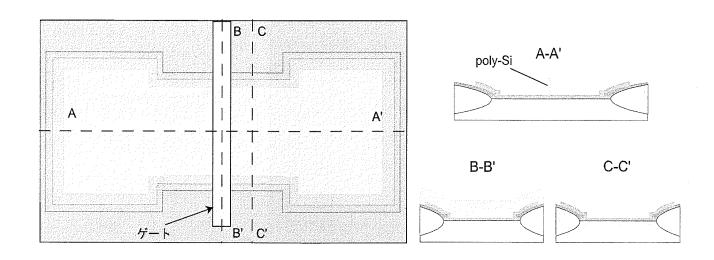

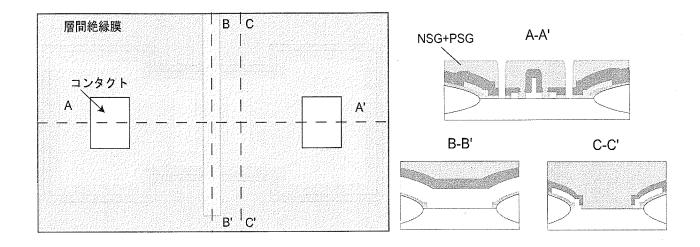

図 2.1 試作したトランジスタの平面図。各試作プロセス段階において、AA'、BB'、CC' 断面を用いて図 2.2 に詳しく述べる。

図 2.2 (1) 試作プロセス (表 2.1 の (1) - (2))

図 2.2 (2) 試作プロセス (表 2.1 の (2) - (5))

図 2.2 (3) 試作プロセス (表 2.1 の (5) - (8))

図 2.2 (4) 試作プロセス (表 2.1 の (9) - (12))

#### 2.2 試作個別プロセス

個々の試作プロセスを以下に順をおって説明する。

#### (1) EB マーク形成

電子線描画装置 (EB) を用いたリソグラフィー工程で重ね合わせ描画を行う際に必要となる EB マークを Si ウエハ上に形成する。このマーク位置を基準として以後のマスクパターン (LOCOS, Cover, Dummy, Gate, Window, Contact, Al) は描画されることになる。

## (2) LOCOS 形成

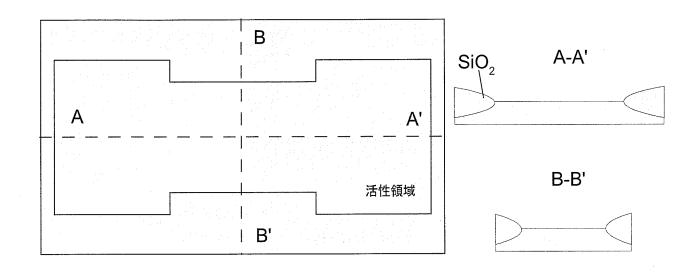

図2.3 LOCOS 形成時の上面図と断面図

まず、Si 表面を熱酸化し、30nm のパッド酸化膜層を形成し、続いて LP-CVD(low-pressure chemical vapor deposition) において厚さ約 120nm のシリコン窒化膜層を堆積した。ここでのパッド酸化膜の役割は、フィールド酸化膜を形成する際に Si の選択酸化時に発生する応力を緩和し、欠陥の発生を防止することにある。パッド酸化膜が厚いほど欠陥の発生防止効果は高いが、あまり厚いと選択酸化時に横方向に酸化が進み、バーズビークと呼ばれる Si 活性層へのフィールド酸化膜の食い込み現象が発生する。

その後、レジストパターンを形成し、CDE(chemical dry etching)を用いて Si 窒化膜のエッチングを行った。レジストを剥離した後、wet 酸化により厚さ 450nm のフィールド酸化膜を形成した。このとき、素子領域は耐酸化性の Si 窒化膜層でマスクされているため、酸化されず、Si が剥き出しの面のみ選択的に酸化される。

#### (3) チャネル・イオン注入

まず、インプラマスク用に酸化を行った (犠牲酸化)。これは、フィールド酸化中に Si 基板に拡散した窒素の除去や、イオン注入時に高速ドーパメントイオンがシリコン表面に 金属汚染等ダメージを与えるので、そのマスクとして行う。

この工程においてチャネル・イオン注入を3度に分けて行った。初めの1回がチャネル

ストップ・イオン注入と呼ばれるものであり、S/D(ソース / ドレイン)間のパンチスルーを抑制するために S/D の拡散深さとほぼ同程度の深さにイオン注入を行う。後の 2 回は 閾値を制御するためのものであり、チャネル表面付近の不純物濃度を低く、バルクの不純物濃度を高くした構造を形成した。この構造により、チャネルの空乏層幅が小さくなり短チャネル効果の抑制が期待できる。

## (4) フィールド酸化膜端保護膜形成

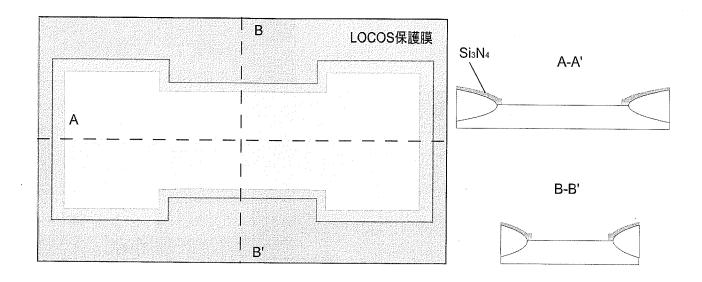

図 2.4 フィールド酸化膜端保護膜時の上面図と断面図

フィールド酸化膜端保護膜用の  $Si_3N_4$  を堆積させる前に、酸化を行い活性領域を 10nm 厚の熱酸化膜で覆う。これは、この後デポする  $Si_3N_4$  は非常に大きな引っ張り応力をもち、直接シリコン基板上に接した場合、その応力のために熱処理によって結晶欠陥が発生するだけでなく、時にはシリコンウェハが割れてしまうほどの力が生じるためである。また、 $Si_3N_4$  をエッチングする際に用いる CDE が  $SiO_2$  と非常に大きな選択比がとれるため、シリコン表面を守るカバー膜としても用いる。

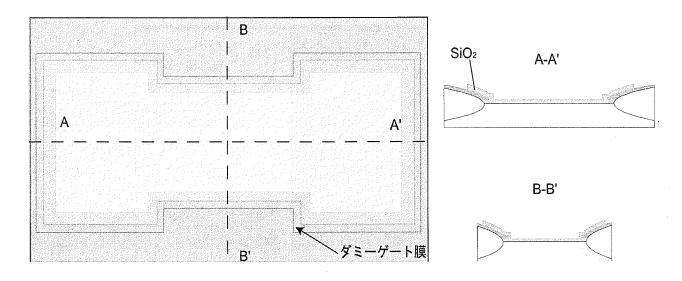

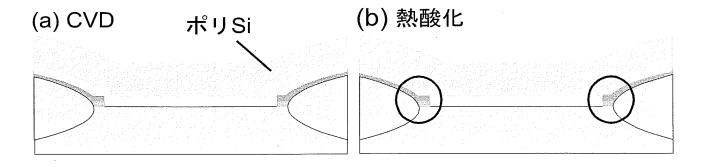

#### (5) ダミーゲート膜形成

図 2.5 に示すように、LPCVD を用いて活性領域を覆うようにに後に除去するダミーゲート膜である HTO(high temperature oxide:  $SiO_2$ ) を堆積する。ここで熱酸化を行わなかった理由としては、熱酸化の場合、以前の工程で堆積させた  $Si_3N_4$  上に酸化膜が形成されず、最終的に完成した際に、非常に耐性の低い部位(図 2.6(b) 丸印)が発生するおそれがあり、デバイスが劣化するおそれがあるためである。

エッチングには、まず RIE(reactive ion etching: 反応性イオンエッチング) を用いてド

図 2.5 ダミーゲート膜形成時の上面図と断面図

ライエッチングを、残りを HF によって溶液エッチングを行うといったように、二段階エッチングを行い  $SiO_2$  を除去した。これは RIE によって Si 基板の表面損傷を抑制するためである。

図 2.6 (a) ダミー膜を CVD で堆積させた場合のゲート形成時の断面図, (b) ダミー膜を熱酸化によって形成した場合のゲート形成時の断面図

#### (6) ゲート形成

ダミーゲート膜上にゲート電極となるポリ Si を LPCVD により堆積する。ゲート電極のシート抵抗や電極形成後のアスペクト比を考慮するとポリ Si 膜は薄いほうが望ましいが、あまり薄いとゲートの配線抵抗の増大やポリ Si を高濃度の  $n^+$  にするために行う  $POCl_3$  気相拡散工程において P のダミーゲート膜や Si 基板への突き抜けが心配されるため十分に膜厚を確保する必要がある。拡散工程後にシート抵抗測定を行い、値が  $34~\Omega$  /  $\square$  であったので不純物が 十分添加されたことが確認できた。その後 Poly-Si 上に LPCVD により HTO を形成し、この HTO を Poly-Si ゲートエッチングのマスクとして用いる。

図 2.7 ゲート形成時の上面図と断面図

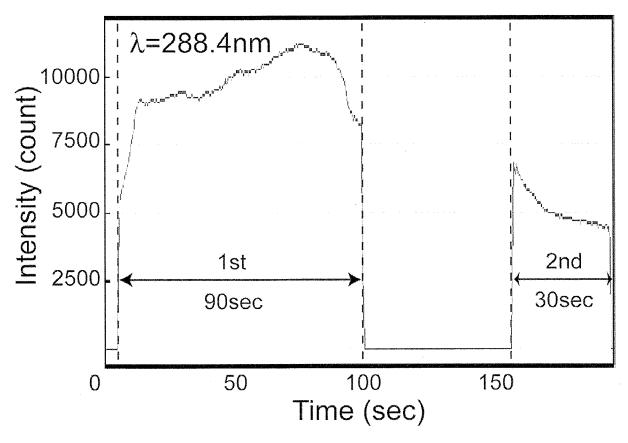

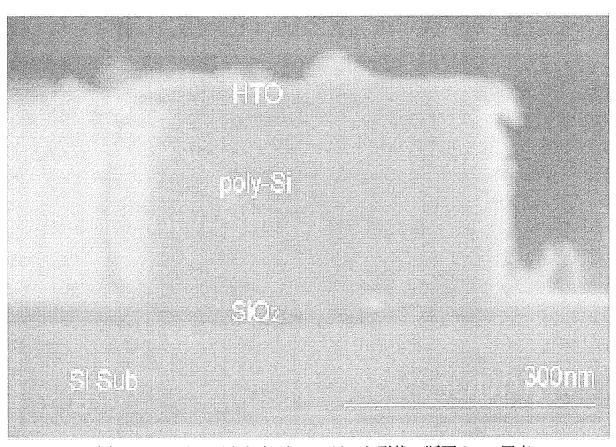

HTO をマスクとした Poly-Si のエッチングは ECR-RIE(electron cyclotron resonance-RIE) を用いる。今回のプロセスではプラズマモニタを用いた 2 段階エッチングを行った。 第 1 段階目のエッチングに用いたガスは  $Cl_2$  に  $N_2$  を添加したもので、ポリ Si 側壁に保護膜を形成させ異方性を重視したエッチング条件である。しかし、この条件ではポリ Si と  $SiO_2$  の十分な選択性が得られないため、 $SiO_2$  が露出し始めたタイミングで第 1 段階目のエッチングをストップし、 $O_2$  を添加することでポリ Si と  $SiO_2$  の間に優れたエッチング選択性が得られる第 2 段階目のエッチング条件に切り替える。しかし、第 2 段階目のエッチングは第 1 段階目よりも異方性が悪化するので、オーバーエッチングによるゲート電極のノッチに注意する必要がある。エッチングガスを切り替えるタイミングはプラズマモニタを用い、エッチング中の発光スペクトルをリアルタイムで観測することで決定した。ポリSi ゲートエッチングで重要となる発光スペクトルは Si を  $Cl_2$  でエッチングすることで生成される SiCl の 288.4nm である。図 2.8 にエッチング中に観測された 288.4nm のスペクトラム強度とエッチング時間の関係、図 2.9 にエッチングされたポリ Si ゲート形状をを示す。

図 2.8 ゲートエッチング時の SiCl(λ=288.4nm) のスペクトラム強度

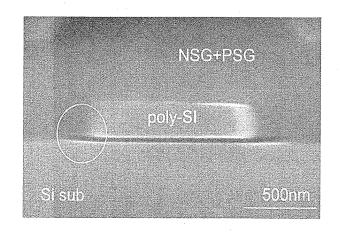

図 2.9 エッチングされたポリ Si ゲート形状の断面 SEM 写真

## (7) 空隙形成

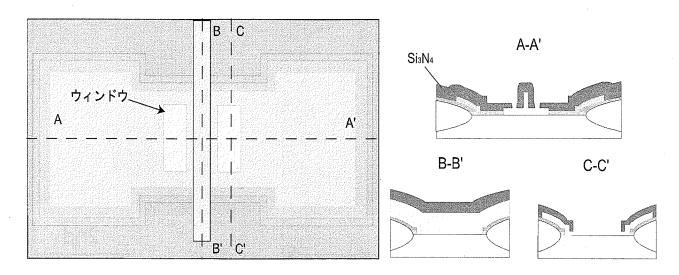

図 2.10 間隙形成時の上面図と断面図

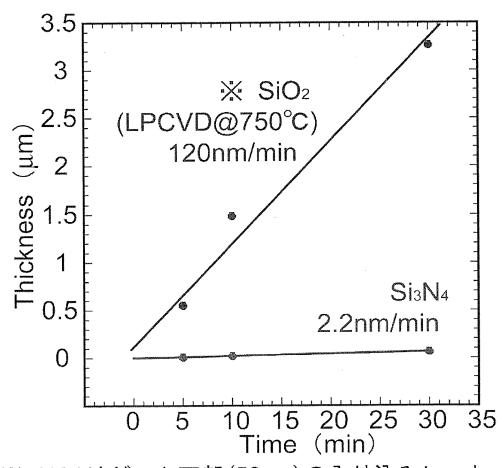

デバイスを作製する前に、まずダミーゲート膜 (HTO) と  $Si_3N_4$  のエッチングレートを調べた (図 2.11)。図 2.10 に示すようにポリ Si ゲートを LOCOS フィールド酸化膜に橋渡しにしたような形を作り、その後 BHF によってエッチングを行った。エッチングをする際、

LOCOS フィールド酸化膜が剥き出しの場合、同時にエッチングされるので、先ほど作製したィールド酸化膜端保護膜が BHF 液の攻撃を守る。これより、選択比が約 54 程度とれることがわかった。

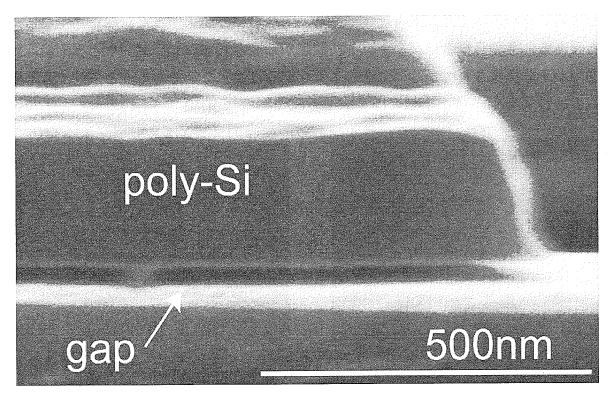

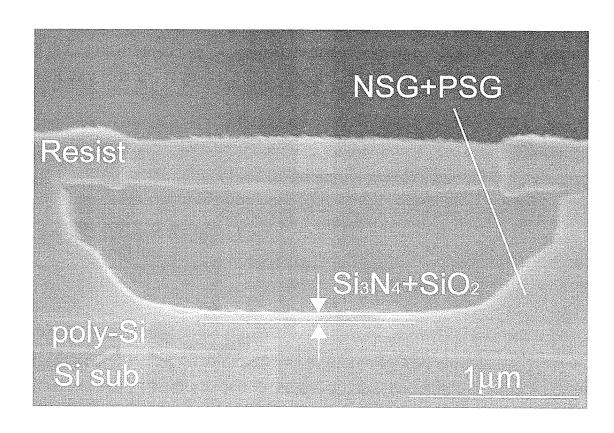

この条件をもちいて本プロセスにおいてはダミーゲート膜の除去を行うが、除去の前にまずゲート下部への層間絶縁膜の入り込みを防ぐために  $\mathrm{Si}_3\mathrm{N}_4$  を堆積する。その後、エッチングウィンドウを形成し RIE で  $\mathrm{Si}_3\mathrm{N}_4$  をエッチングする。ここではより垂直性を得たいために等方性の CDE を用いず、RIE を用いてエッチングを行った。また、エッチングの進行具合を制御するためウィンドウとゲートとの距離を  $500\mathrm{nm}$  とした。得られたゲート周りの形状を図 2.12 に示す。

ダミー膜を除去した後、層間絶縁膜 PSG(phosphorus silicate glass) 及び NSG(nondoped silicate glass) を APCVD(atmospheric-pressure chemical vapor deposition) により堆積する。PSG にはトランジスタに有害な Na<sup>+</sup> などのアルカリイオンのゲッタリング効果がある。

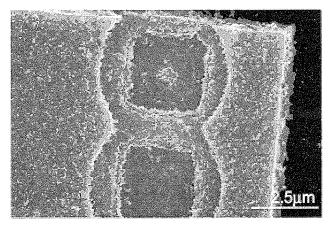

図 2.13 にウィンドウリソ後と層間絶縁膜堆積後の上面写真を示す。層間絶縁膜が堆積された後でも、ダミーゲート膜が BHF によってウェットエッチングによってダミー膜が円形状に除去されたあとが見てとれる。これよりゲートまわりのダミー膜が十分除去されたことが確認できる。

※ SiO2はゲート下部(50nm)の入り込みレート

図 2.11 BHF による HTO と  $Si_3N_4$  のエッチングレート

図 2.12 ダミー膜エッチング後断面 SEM 写真

図 2.13 ウィンドウリソ後(左)と層間絶縁膜堆積後(右)

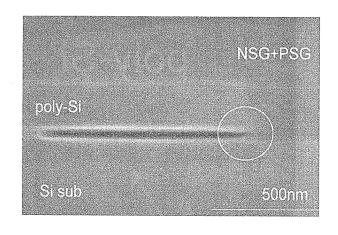

また、 $Si_3N_4$  膜を堆積せずにダミーゲート膜を除去したものと  $Si_3N_4$  を堆積させた後ウィンドウを形成しダミーゲート膜の除去を行い、層間絶縁膜を堆積させたものの比較を図 2.14 に示す。前者のほうはゲート下部に約 50nm 程度層間絶縁膜が入り込んでいることがわかる。このような状態ではゲートに接している層間絶縁膜を介して MOS 構造が形成されてしまい、絶縁破壊を起こす可能性がある。これでは間隙を作った意味が無くなってしまうと言える。その点後者はゲート以前に間隙が形成されており、ゲートと層間絶縁膜の間に間隙が十分確保されているのでそのような問題は生じないであろうと予測できる。

図 2.14 層間絶縁膜入り込み比較図 (左 Si<sub>3</sub>N<sub>4</sub> 膜堆積無、右 Si<sub>3</sub>N<sub>4</sub> 膜堆積有)

ダミー膜を除去した後、層間絶縁膜 PSG(phosphorus silicate glass) 及び NSG(nondoped silicate glass) を APCVD(atmospheric-pressure chemical vapor deposition) により堆積する。PSGにはトランジスタに有害な Na<sup>+</sup>などのアルカリイオンのゲッタリング効果がある。

## (8) コンタクト形成

図 2.15 コンタクト形成時の上面図と断面図

今回のプロセスではコンタクトホールを活性領域およびゲートまで掘るために、

- ① SiO<sub>2</sub> (NSG+PSG)

- ② Si<sub>3</sub>N<sub>4</sub> (ウィンドウ形成用ゲート下部保護膜)

- ③ SiO<sub>2</sub> (ダミー膜およびゲート用ハードマスク)

#### の3段階の膜をエッチングする必要がある。

①の膜において RIE + BHF のドライ+ウェットの 2 段階エッチングを行った。これは②の膜をエッチングする際に①の膜が残っていた場合、 $SiO_2$  が  $Si_3N_4$  のマスクとなり  $Si_3N_4$  が十分にエッチングされない可能性があるためである。また、RIE のエッチングレートの面内均一性を考慮に入れた場合、ウエハ中心部と外側のエッチングレートの違いが生じるため、外側に残膜が生じ、それを  $SiO_2$  と  $Si_3N_4$  の選択比がよりとれる BHF によるウェットエッチで補正するといった目的もある。(BHF のエッチングレートは図 2.11 を参照)

図 2.16 コンタクトホール第1段階エッチング後

①の膜がエッチングし終わった状態を確認し(図 2.16)、②の膜がむきだしになっているのでこれを RIE によってエッチングする。③の膜は BHF によってエッチングを行うので、②の膜は残膜が生じないように外側のレートにあわせて十分にエッチングを行う。この場合、中心部がオーバーエッチングされてしまうが③の膜がマスクとなり基板に損傷が入ら

図 2.16 コンタクトホール第1段階エッチング後

①の膜がエッチングし終わった状態を確認し(図 2.16)、②の膜がむきだしになっているのでこれを RIE によってエッチングする。③の膜は BHF によってエッチングを行うので、②の膜は残膜が生じないように外側のレートにあわせて十分にエッチングを行う。この場合、中心部がオーバーエッチングされてしまうが③の膜がマスクとなり基板に損傷が入らない。その後③の膜は BHF で補正しコンタクトを形成した。

# (9) Al 電極形成

図 2.17 Al 形成時の上面図と断面図

コンタクトホール形成後、スパッタ法において Al を 700nm 堆積した。直前に HF 溶液 によってコンタクト表面にできた自然酸化膜を除去しておく。

Al エッチングを溶液エッチングで行い、その後剥離液をもちいてレジストを除去する。 レジスト剥離液による Al のダメージを図 2.18 に示す。レジスト剥離直後の Al 側面には エッチング時にできた段差が確認できるが、さらに剥離液に浸透した場合その段差部分も 削れ、角も丸くなっているのが確認できる。この段階ではまだ Al の断線は確認できないが、 長時間剥離液に浸透していると、Al が断線してしまうことを示唆している。

(a) レジスト剥離直後 (b) 追加して剥離液に浸透 図 2.18 レジスト剥離液による Al 膜の薄層化

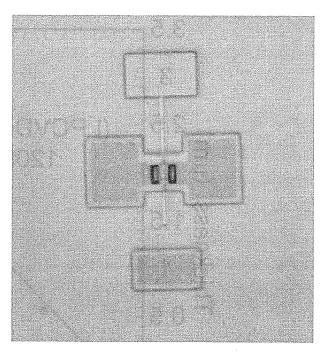

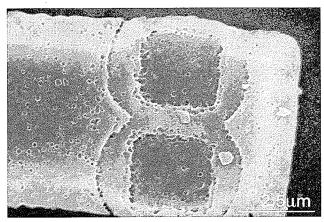

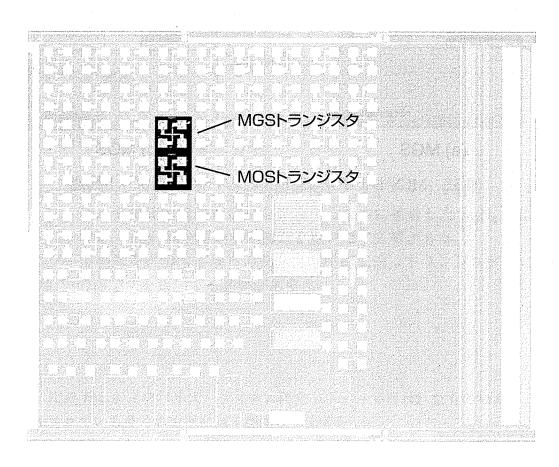

以上、詳細に述べたプロセス工程を通って完成したトランジスタの俯瞰図を図2.19示す。なお、この MGS トランジスタと比較するため、ダミーゲート膜を除去する工程を省いた MOS トランジスタも同じウェハの中に形成した。ダミーゲート膜をエッチングする際に、MOS トランジスタ形成部分はレジストで覆っておく。

図 2.19 完成した MGS(metal-gas-semiconductor:金属 – 気体 – 半導体 トランジスタ)の SEM 俯瞰写真

#### 第3章 試作した TEG パターンと完成したウェハ

TEGとは、test element group の略称で、製品を開発する段階において、様々なプロセス条件、デバイス条件を設定するために試作するパターンのことである。プロセスTEG、デバイスTEG、信頼性TEG、歩留まり向上TEG、製品そのもののTEGなど多くの種類がある。本研究の段階は、まだ世の中にないトランジスタ構造を試作するためのものであるから、もっとも早い時期のプロセス・デバイスTEGと言える。

#### 3.1 TEG パターン

本研究で作製した MGSFET は全てリソグラフィ工程を電子線描画装置を用いて行った。リソグラフィーを行うにはマスクパターンの設計が必要である。ここでは設計したマスクパターンの内容を説明する。今回の作製の目的は MGSFET のプロセスの構築とその評価を行うことである。

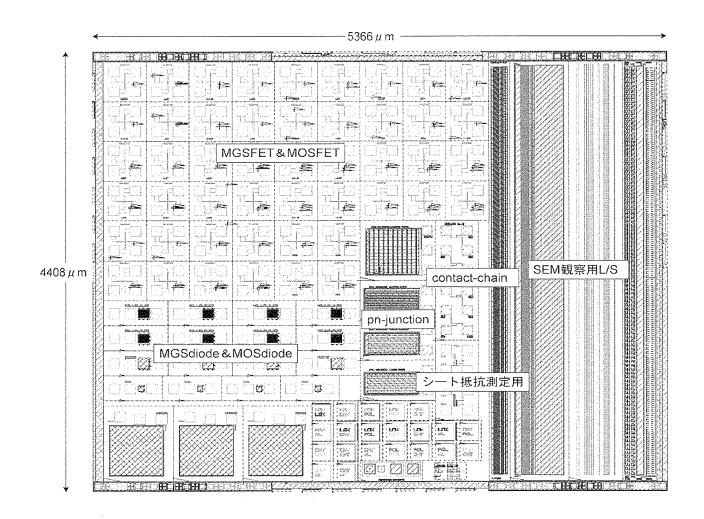

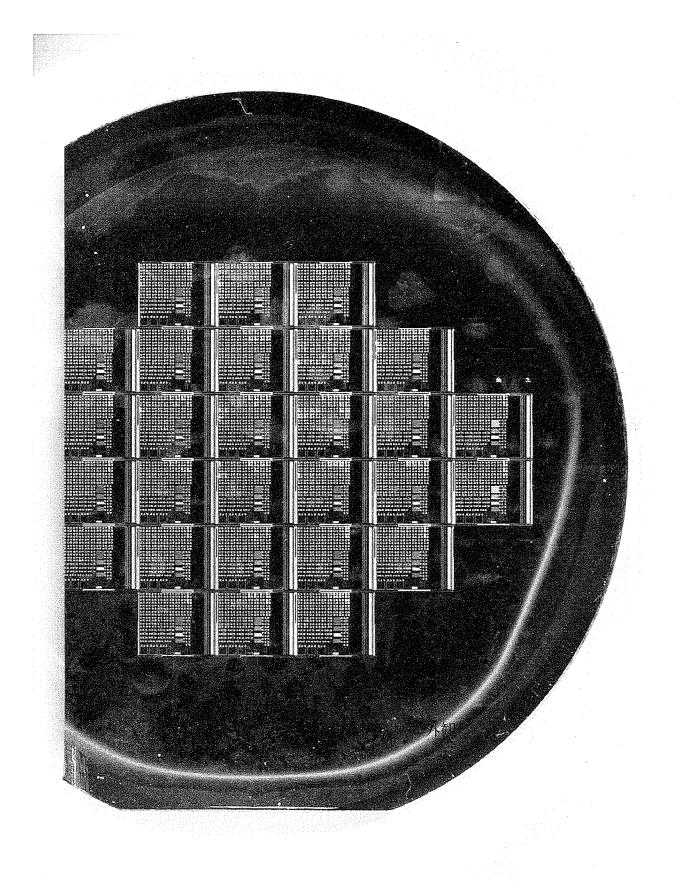

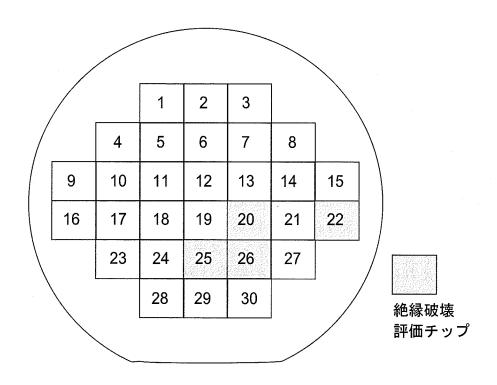

図 3.1 にチップ全体のマスクパターンレイアウトを示す。このチップを 2 インチ Si ウエハ上に 30 チップ作製した。

図 3.1 作製した TEG レイアウト・チップ全体図

組み込んだ組み込んだパターンは大別して下記の8種類である。マスク合わせは計8回 行う。

- ① MGSFET

- ② MOSFET

- ③ MGS ダイオード

- ④ MOS ダイオード

- ⑤コンタクト・チェイン

- ⑥ pn 接合

- ⑦シート抵抗測定用パターン

- ⑧ SEM 観察用 L/S

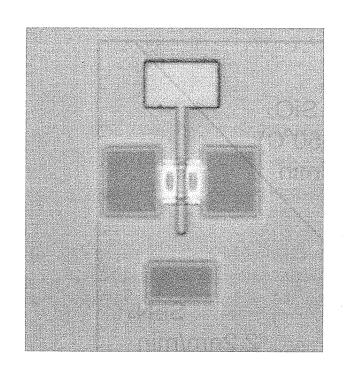

図 3.2 に MGSFET のレイアウト図を示す。コンタクト径は  $2\mu m$  である。また LOCOS カバー膜と LOCOS 酸化膜のオーバーラップを  $1\mu m$  と余裕をもって設計した。また LOCOS 酸化時に選択酸化によって生じるバーズビークが、垂直方向につく  $SiO_2$  と同程度だけ水平方向にも入り込むことを考慮し、ダミー膜と LOCOS とのオーバーラップは  $0.5\mu m$  とした (LOCOS 酸化膜厚は  $0.45\mu m$ )。この条件によって、バーズビーク上部からのゲート 絶縁破壊による耐圧は守られることが予想される。

図 3.2 MGSFET レイアウト図

TEG に組み込んだ MGS および MOS トランジスタのゲート長とゲート幅の組み合わせの一覧を表 3.1 に示す。中心をゲート長: $L=1\mu m$ 、ゲート幅: $W=5\mu m$  とした。

表 3.1 TEG に組み込んだトランジスタのゲート長とゲート幅の組み合わせ

| MGSFET    |    |      | <i>L</i> (μm) |      |     |      |     |      |     |      |     |     |     |   |     |     |   |   |   |

|-----------|----|------|---------------|------|-----|------|-----|------|-----|------|-----|-----|-----|---|-----|-----|---|---|---|

|           |    | 0.05 | 0.1           | 0.15 | 0.2 | 0.25 | 0.3 | 0.35 | 0.4 | 0.45 | 0.5 | 0.7 | 8.0 | 1 | 1.2 | 1.5 | 2 | 3 | 5 |

| W<br>(µm) | 2  |      |               |      |     |      |     |      |     |      |     |     |     | 1 |     |     | 1 |   |   |

|           | 5  | 1    | 1             | 1    | 1   | 1    | 1   | 1    | 1   | 1    | 1   | 1   | 1   | 2 | 1   | 1   | 2 | 1 | 1 |

|           | 10 |      |               |      |     |      |     |      |     |      |     |     |     | 1 | ·   |     | 1 |   |   |

| MOSFET           |    |      | <i>L</i> (μm) |      |     |      |     |      |     |      |     |     |     |   |     |     |   |   |   |

|------------------|----|------|---------------|------|-----|------|-----|------|-----|------|-----|-----|-----|---|-----|-----|---|---|---|

|                  |    | 0.05 | 0.1           | 0.15 | 0.2 | 0.25 | 0.3 | 0.35 | 0.4 | 0.45 | 0.5 | 0.7 | 0.8 | 1 | 1.2 | 1.5 | 2 | 3 | 5 |

| <i>W</i><br>(μm) | 2  |      |               |      |     |      |     |      |     |      |     |     |     | 1 |     |     | 1 |   |   |

|                  | 5  | 1    | 1             | 1    | 1   | 1    | 1   | 1    | 1   | 1    | 1   | 1   | 1   | 2 | 1   | 1   | 2 | 1 | 1 |

|                  | 10 |      |               |      |     |      |     |      |     |      |     |     |     | 1 |     |     | 1 |   |   |

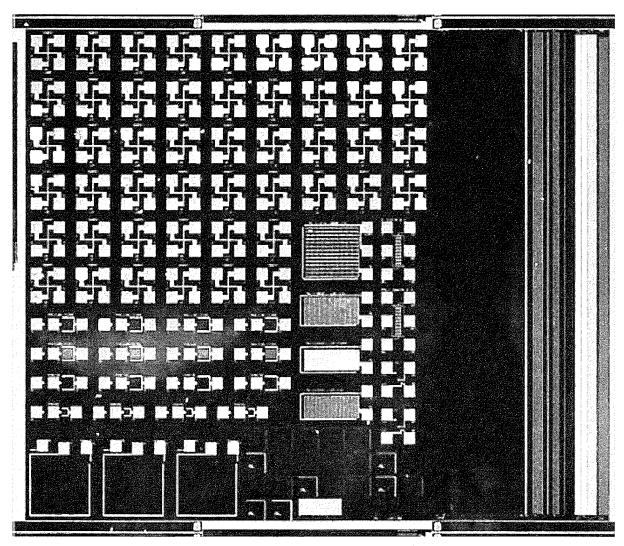

# 3.2 試作したウェハとチップの外観

図3.3 試作したチップの外観

図 3.4 完成した 50mm<sup>®</sup> 試作ウェハの外観。 ウェハ上に 30 のチップを造りつけた。向かって左端は SEM 観察のために切り取っている。

## 第4章 トランジスタ特性評価

本章では、作製したトランジスタの特性を評価する。今回作製したデバイスは MGS-FET および、比較用の MOSFET である。基板に  $50\text{mm}^{\phi}$  シリコン基板、p 型で面方位が (100)、抵抗率が  $8\sim12\Omega$ -cm のものを使用した。また MGSFET と MOSFET は共に物理的なゲート膜厚は 50nm で同じである。

## 4.1 電実効チャネル長の算定

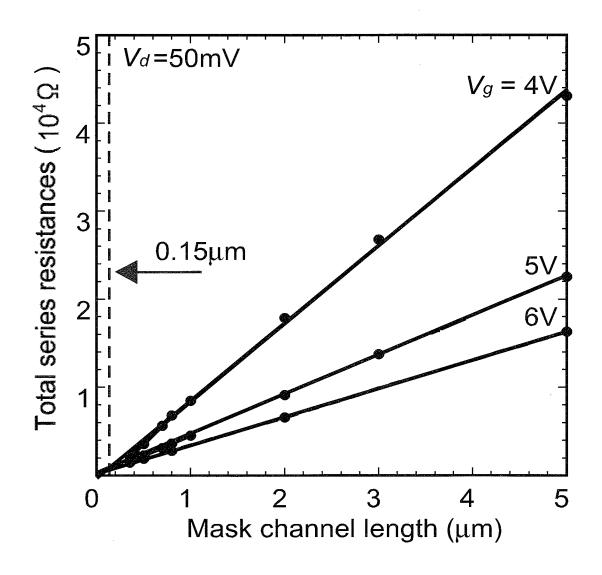

測定を始めるに当たって、実効チャネル長の縮小を調べた。図 4.1 は MOSFET の  $W=9\mu$ m,  $V_d=0.05$ V におけるソース - ドレイン間直列抵抗値をゲート電圧  $V_g$  を変化させ ゲート長に対してプロットしたものである。このように  $V_g$  が十分高く, $V_d$  が非常に低い バイアス条件においてチャネルは抵抗と見なすことができる。このことより  $V_g$  を変化させた場合、その直線は共通交点を持ち、その時のL の値がプロセスによって縮小されたチャネル長  $\Delta L$  であり、L -  $\Delta L$  が実効チャネル長:  $L_{\rm eff}$  となる。

図 4.1 チャネル抵抗法による AL の導出

図 4.1 より ΔL はほぼ 0.15μm であることが見て取れる。縮小の原因として

- (1) ゲートエッチング工程において、マスクである HTO をエッチングした際にドライエッチングを行った後に溶液エッチングを行ったために、HTO が等方エッチングされマスクが縮小。

- (2) ゲート電極のポリ Si エッチング時に二段階目のエッチングが垂直性が乏しいため 横方向にもエッチングされゲートが縮小。

- (3) S/D 注入時における横方向拡張 の三種類が推測される。

## 4.2 $I_{d}$ - $V_{d}$ 特性および $I_{d}$ - $V_{g}$ 特性

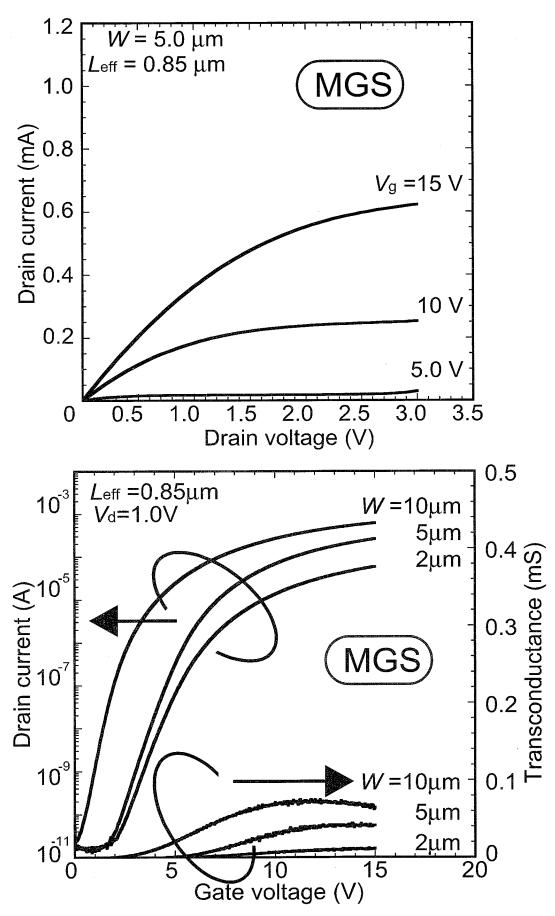

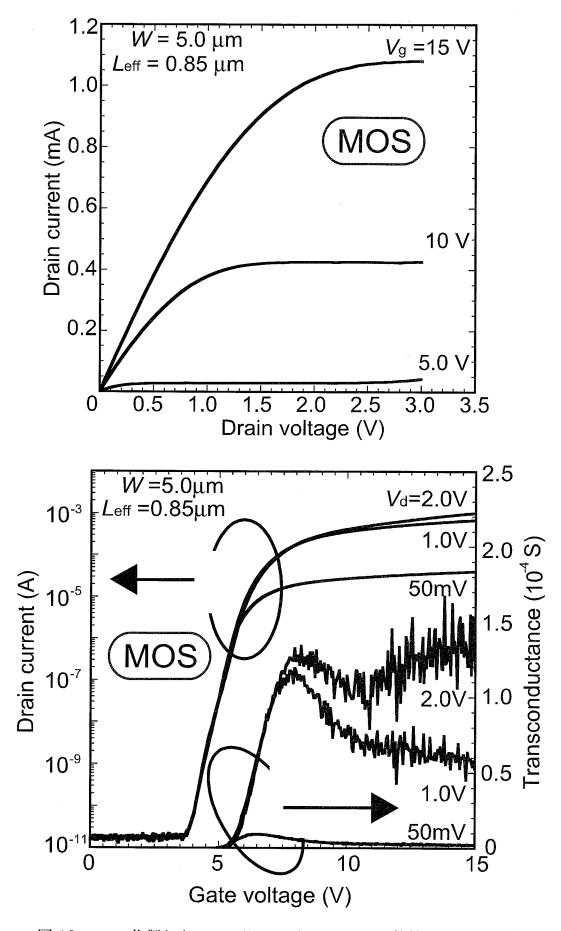

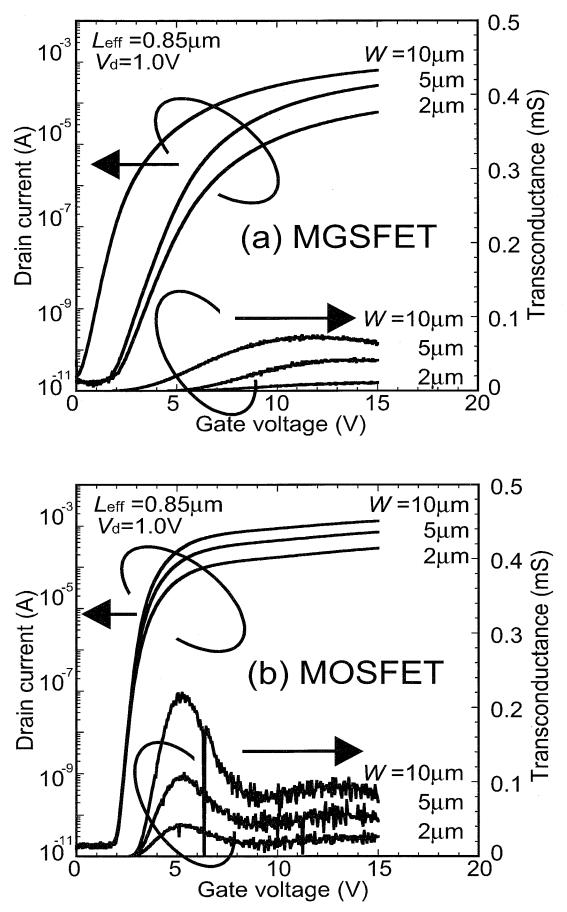

作製した MGSFET と MOSFET の  $I_{\rm d}$ - $V_{\rm d}$  特性および  $I_{\rm d}$ - $V_{\rm g}$  特性をそれぞれ図 4.2(a) と図 4.2(b) に示す。それぞれのデバイスパラメータは実効チャネル長  $L_{\rm eff}=0.85\mu{\rm m}$ 、ゲート幅  $W=5.0\mu{\rm m}$  である。またトランジスタのパラメータにおいて最も重要なものの一つとして、トランスコンダクタンス  $g_{\rm m}$  が挙げられる。その値は

$$g_m = \frac{\partial I_d}{\partial V_g} |_{V_d = -\hat{\pi}} \tag{4.1}$$

で与えられ、ゲート電圧がドレイン電流を制御する重要なパラメータとなっており、その値が最大値を取る点がそのデバイスにおいてドレイン電流の傾きが最も急峻になっている。 $g_{\rm m}$ の値も図 4.2 に同時に示す。

MOSFET に比べて、MGSFET は電流値は低く、サブスレッショルド領域での立ち上がりもなだらかであるが、遮断領域と動作領域での電流値の差が十分大きく、トランジスタ動作が確認できたといえる。以下の節で、その理由等を考察していく。

図 4.2 (a) 作製した MGS トランジスタの  $I_{\rm d}$ - $V_{\rm d}$  特性および  $I_{\rm d}$ - $V_{\rm g}$  特性

図 4.2 (a) 作製した MOS トランジスタの  $I_{\rm d}$ - $V_{\rm d}$  特性および  $I_{\rm d}$ - $V_{\rm g}$  特性

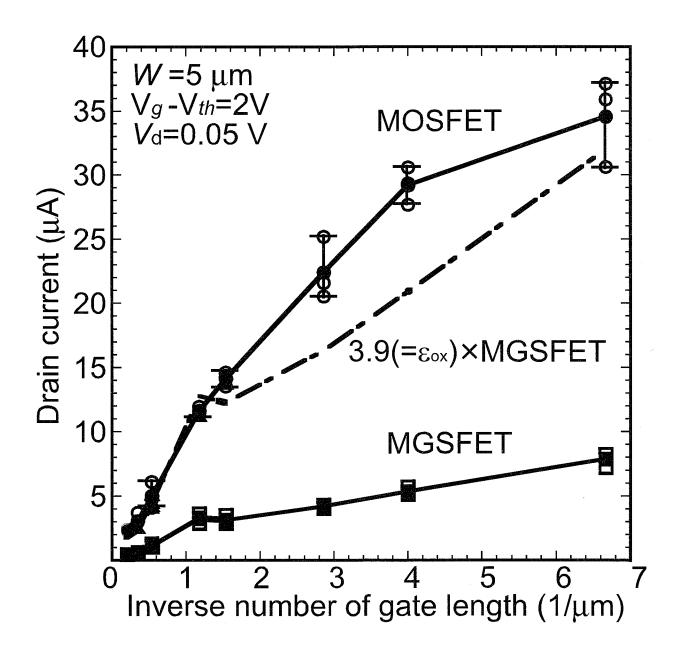

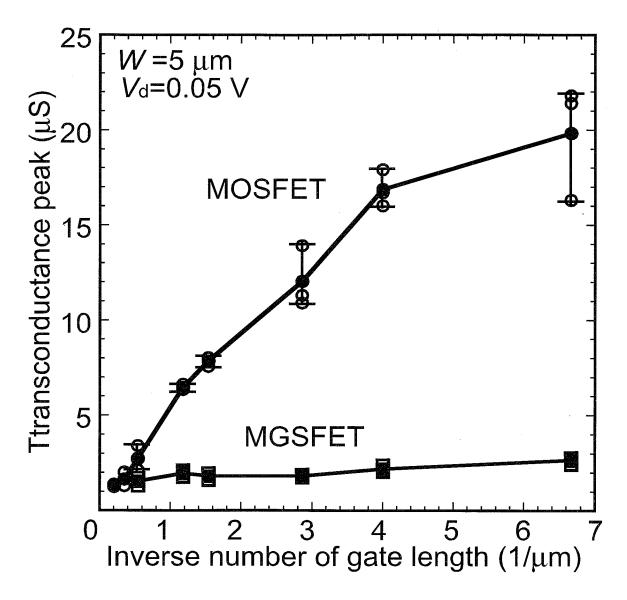

## 4.3 電流駆動能力

作製した MGSFET と MOSFET の電流駆動能力を図 4.3 に示す。 $V_{\rm d}$  が  $V_{\rm g}$ - $V_{\rm th}$  より十分小さい場合には、ドレイン電流は

$$I_d = \mu \frac{\varepsilon \cdot \varepsilon_0}{d} \frac{W}{L} (V_g - V_{th}) V_d \tag{4.2}$$

で定義される。ここで、 $\mu$  はキャリアの移動度、 $\epsilon$  は比誘電率、 $\epsilon_0$  は真空の誘電率、 $\epsilon$  はゲート絶縁膜厚である。

図 4.3 電流駆動能力のゲート長依存性

今回作製した MGSFET と MOSFET はゲート絶縁膜厚 d は同じ値であるので、図 4.3 での測定点において MGSFET のドレイン電流は MOSFET との比誘電率の商、つまり MOSFET のゲート膜である  $SiO_2$  の比誘電率が 3.9 であることから、MGSFET の間隙の 比誘電率を 1 であると仮定すると、1/3.9=約25% 程度であるのが正常であると言える。 図 4.3 において、ゲート長依存性の駆動力では MGSFET の電流値は MOSFET の 18.7% ~ 28.2% 得ることができ、ほぼ正常な電流駆動能力が得ることができたといえよう。

#### 4.4 最大トランスコンダクタンス

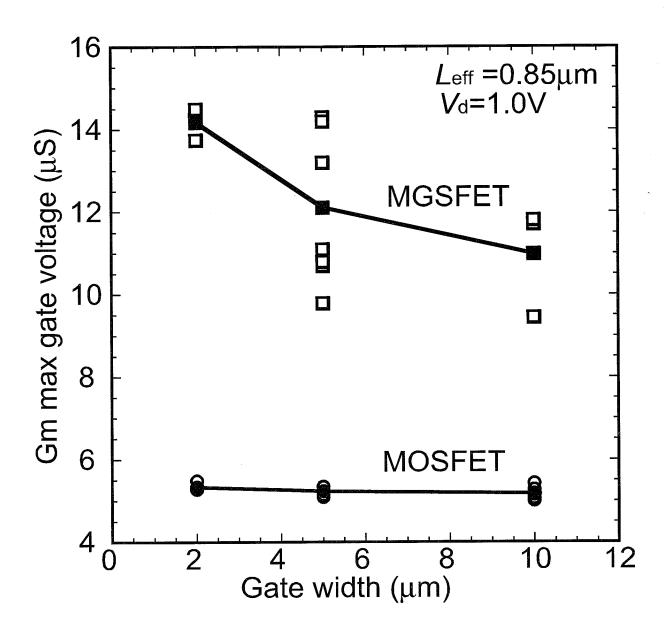

4.1.2 節でも述べたようにトランスコンダクタンスはゲートがトランジスタにとってその立ち上がり特性を示す非常に重要なパラメータとなっている。この節では、その最大値と最大値でのゲート電圧について考察する。

図 4.4 トランスコンダクタンスの最大値 - ゲート幅依存性

図 4.4 にトランスコンダクタンスの最大値 - ゲート幅依存性を、図 4.5 にその最大値時のゲート電圧 - ゲート幅依存性を示す。MOSFET と MGSFET 共にゲート幅が大きくなるにつれてその最大値が上昇していることが確認できる。また、MGSFET の最大値は同じゲート長の MOSFET と比べてゲート長が短い領域では  $12.9\% \sim 23.2\%\%$  の値を示した。これは 4.1.4 節で考察した、電流駆動能力のの 25% という値に比べて、やや低い値であるといえる。しかしながら、ゲート長の長い領域では  $30\% \sim 56.3\%$  という非常に高い値を示した。

図 4.5 トランスコンダクタンスの最大値時のゲート電圧 - ゲート幅依存性

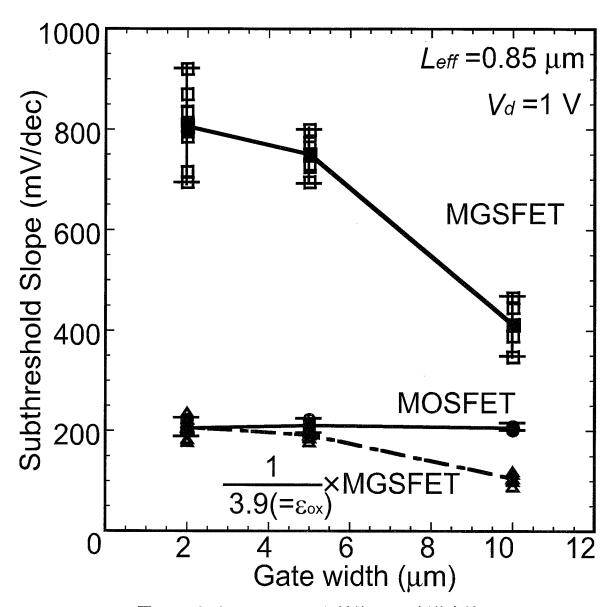

#### 4.5 サブスレッショルド係数

ゲート電圧がしきい値電圧より低く、半導体表面がわずかしか反転していない場合のドレイン電流はサブスレッショルド電流と呼ばれる。実際の回路中ではトランジスタが低電力デバイスとして用いられる場合、この領域での電流がスイッチのオン・オフの決定をしており、その傾きは急峻なほどスイッチングに優れたものであるといえる。

サブスレッショルド係数Sはその傾きを表すものであり、MOSFETにおいてその値は

$$S = \ln 10 \cdot \frac{kT}{q} \left( 1 + \frac{C_D}{C_{ox}} \right) \tag{4.3}$$

で定義される。ここで、k はボルツマン定数、 $C_D$  は空乏層容量、 $C_{OX}$  はゲート酸化膜容量である。サブスレッショルド係数の単位は (mV/decade) であり、サブスレッショルド領域での立ち上がりにおいて一桁電流が変化するのに要するゲート電圧を表している。式 4.3 において  $C_D/C_{OX}$  が無視できる場合には、よく知られているように、S は基板の物質に固有の値を示し、シリコンの場合には 60mV/decade となる。

作製した MGSFET と MOSFET の異なるゲート幅における  $I_{\rm d}$ - $V_{\rm g}$  特性を図 4.6 に示す。 MOSFET ではサブスレッショルド係数はどのゲート幅でも一定であるが、MGSFET は ゲート幅が大きくなるに連れて、立ち上がりが急峻に、つまりサブスレッショルド係数が 低くなっているのが確認できる (図 4.7 参照)。しかしながら、式 (4.3) より、サブスレッショルド係数はゲート幅には依存せず、ゲート厚容量および空乏層容量のみに依存している。ここで、図 4.8 のようにもし 5i と間隙の間に自然酸化膜等なんらかの界面準位が存在し、その欠陥密度が非常に高いものであれば、それが空乏層容量と直列に繋がった容量としてふるまうので、直列に繋がった容量としてふるまうので、サブスレッショルド係数は式 (4.3) で与えられるものよりも寝たものとなる可能性がある。しかしながらこれはゲート幅に依存したものとは言えず、今回観測された波形の原因であるとは言い難い。ゲート幅に依存した別の原因があると考えられ、その原因を今後解析していく予定である。

図 4.6 異なるゲート幅における  $I_{

m d}$ -V $_{

m g}$  特性

図 4.7 サブスレッショルド係数ゲート幅依存性

図 4.8 MGSFET と MOSFET の寄生容量モデル

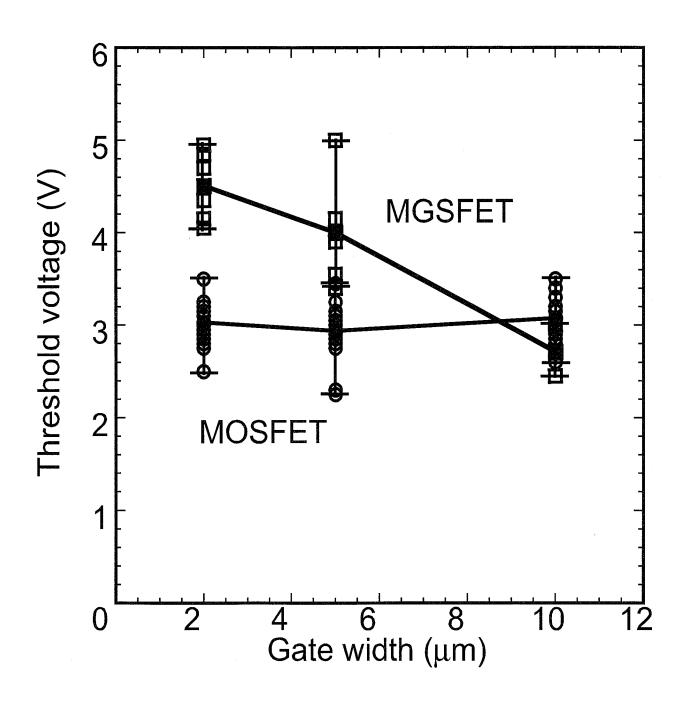

## 4.6 しきい電圧

作製した MGSFET と MOSFET のしきい値電圧ゲート幅依存性を図 4.9 に示す。 しきい値電圧は

$$V_{th} = V_{g_{(I_d = \frac{W}{L} \times 0.1 \mu A)}} \tag{4.4}$$

と定義している。

図 4.9 しきい値電圧ゲート幅依存性

MOSFET のしきい値電圧はゲート幅に依存せずほぼ同じ値を示しているが、MGSFET はゲート幅が大きくなるにつれてしきい値電圧が減少しているのが確認できる。これは、前節で考察したサブスレッショルド係数と非常に密な相関関係にあるといえる。サブスレッショルド係数が高ければドレイン電流の立ち上がりが緩やかなので、立ち上がり始めからしきい値電圧にまで達する電圧が余分に印加される必要がある。これにより、しきい値電圧がゲート幅の増加と共に減少していると考えられる。

## 第5章 強制破壞試験結果

本研究の主な目的は固体のゲート絶縁膜が存在しないことによるゲート耐圧の向上である。アノード(陽極)とカソード陰極)の間が高真空である真空管は放射線や宇宙線に非常に大きな耐性があることがわかっている。それと類似の特長を本MGSトランジスタに期待している。

一方、適度な圧力の気体が存在すると容易に気体放電が発生するが、これは気体分子や原子間の距離が適当に長いと、分子や原子を電離するに十分なエネルギを電子が得るからで、圧力を高める、あるいは電極間距離を短くすれば放電を抑制することができる。実際、高電圧の遮断器や、電力トランスには高圧のSF<sub>6</sub> ガスが用いられている。

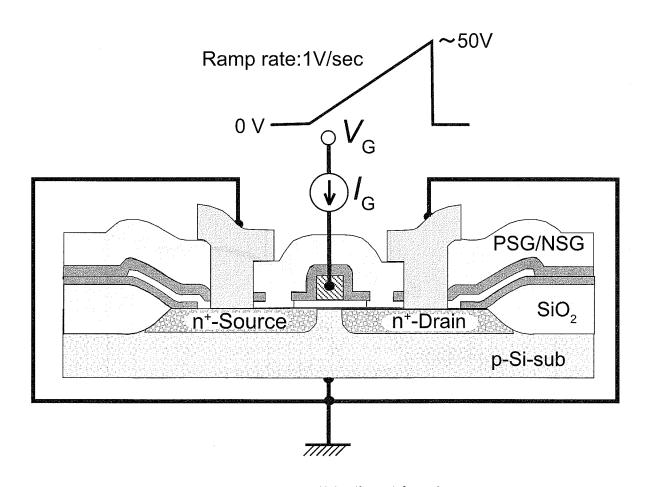

#### 5.1 測定回路

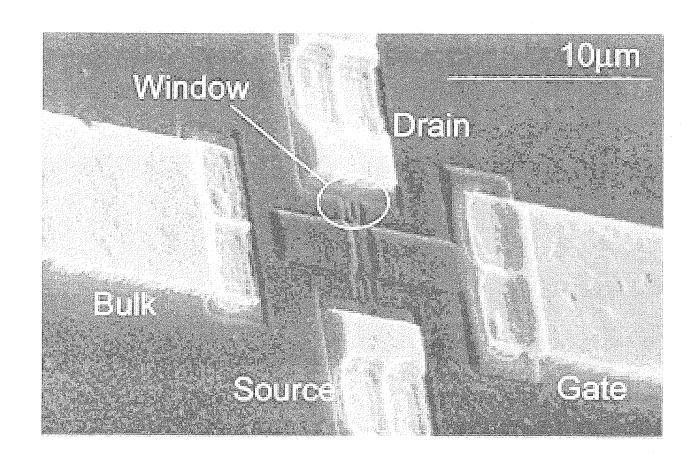

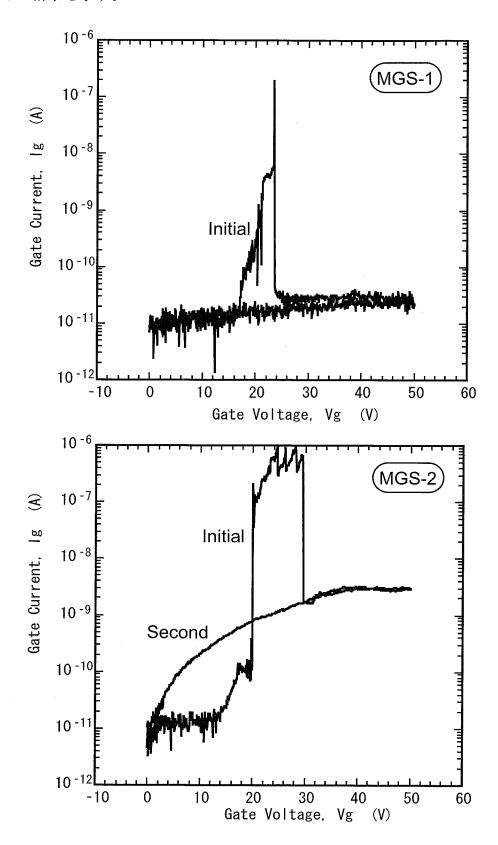

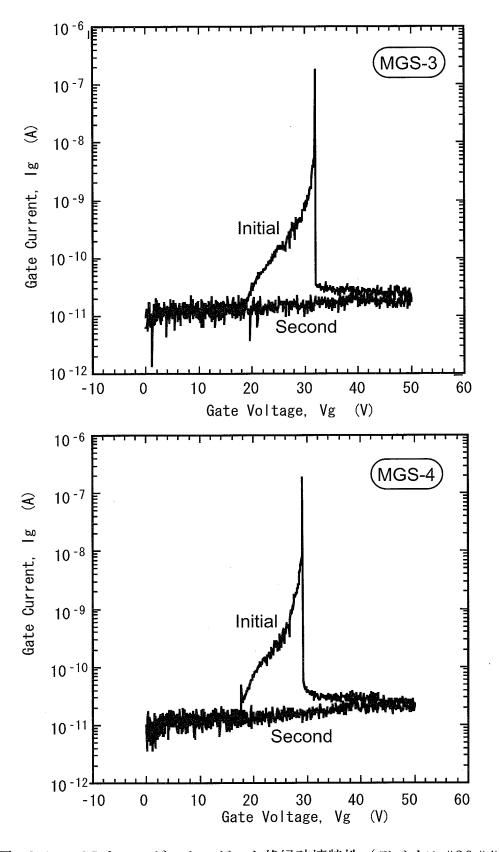

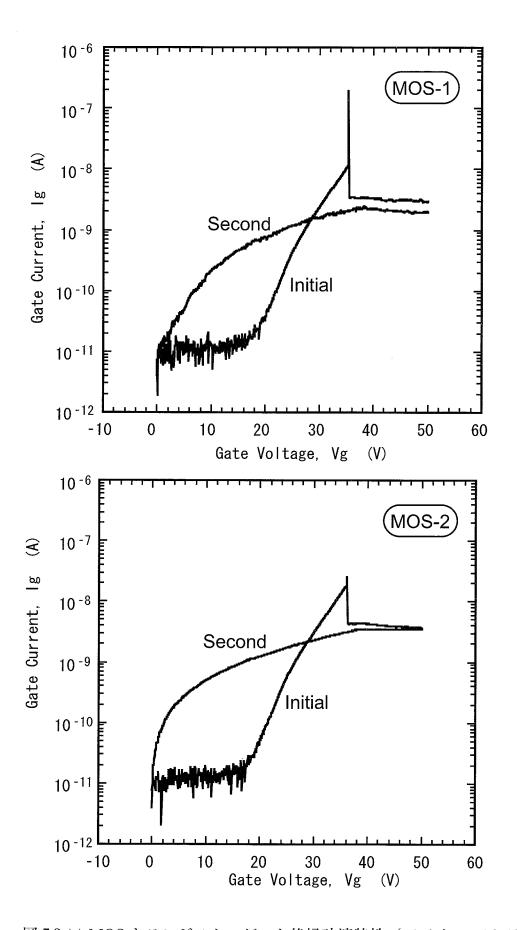

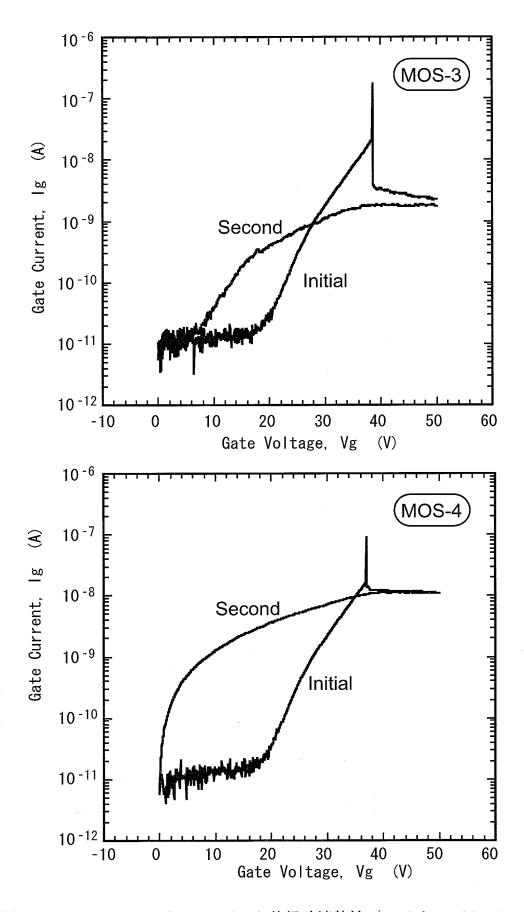

図 5.1 に示す結線によって MGS と MOS トランジスタのゲートにランプ電圧を印加し強制的にゲート絶縁を破壊した。図 5.2 に MGS トランジスタの結果を、図 5.3 にMOS トランジスタの結果を図示する。

図中で、破壊した最初の印加を"initial"と名付け、破壊した後に再び印加して破壊状態を確かめた二回目の印加を"second"として図示した。

図 5.1 ゲート絶縁耐圧測定回路

## 5.2 ゲート絶縁強制破壊試験

図 5.1 に示したセットアップで MGS および MOS トランジスタを 4 個ずつ破壊した。図 5.2 と図 5.3 にその結果を示す。

図 5.2 (a) MGS トランジスタのゲート絶縁破壊特性 (デバイス #1&#2)

図 5.2 (b) MGS トランジスタのゲート絶縁破壊特性 (デバイス #3&#4)

図 5.3 (a) MOS トランジスタのゲート絶縁破壊特性 (デバイス #1&#2)

図 5.3 (b) MOS トランジスタのゲート絶縁破壊特性 (デバイス #3&#4)

図 5.2 と図 5.3 を比べて明らかな差がある。MOS トランジスタは従来のよく知られた特性で、一度ゲート破壊を起こすとゲート絶縁膜には恒常的な導電経路ができ、トランジスタとしては動作しない。

いっぽう、MGS は一度破壊すると、恒常的な導電経路は消失し、あたかもゲートが優れた絶縁性を示す。デバイス#2は4個破壊したトランジスタの内の1個だから、トランジスタそのものがまともにできていなかったと考えて良いだろう。ゲート下にわずかでも除去しきれずに酸化膜が残っていれば MOSトランジスタと同じような特性を示すと考えられるからである。

図 5.4 MGS および MOS トランジスタのゲート絶縁破壊特性のまとめ

## 5.3 ゲート絶縁強制破壊後のトランジスタ特性

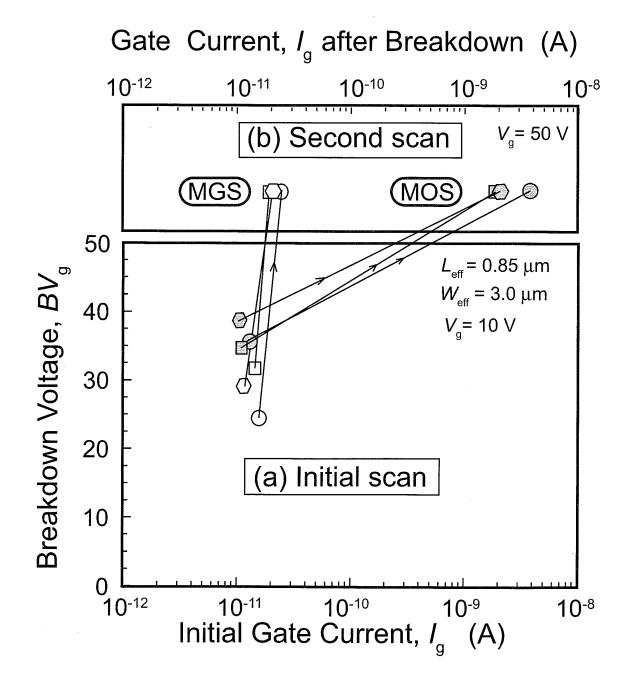

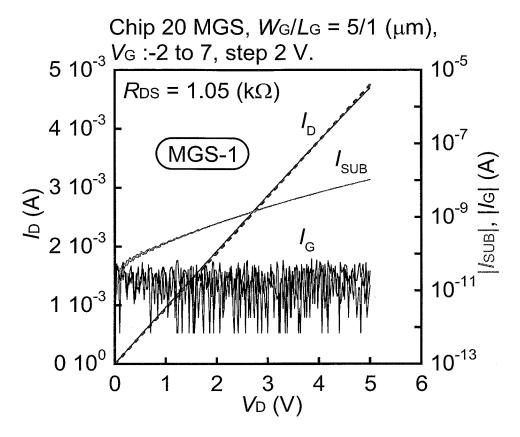

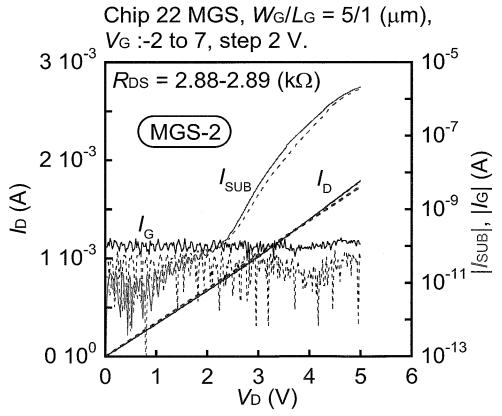

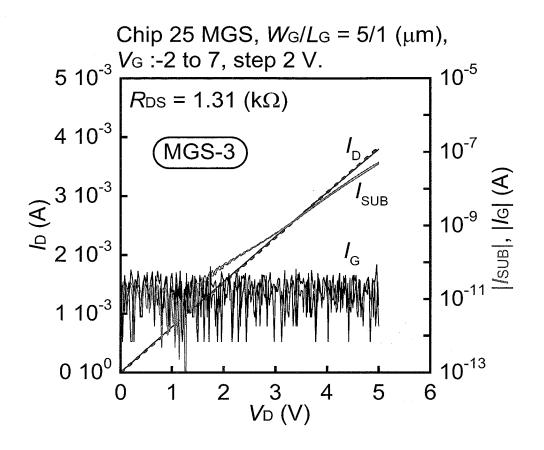

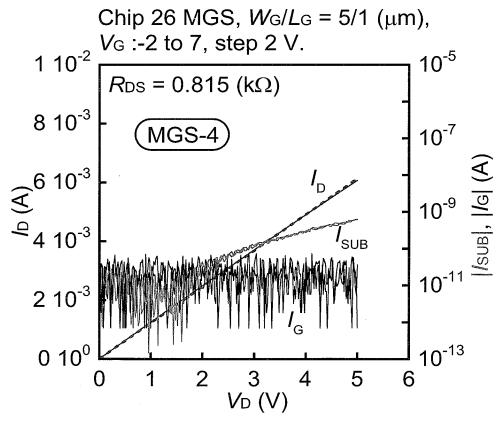

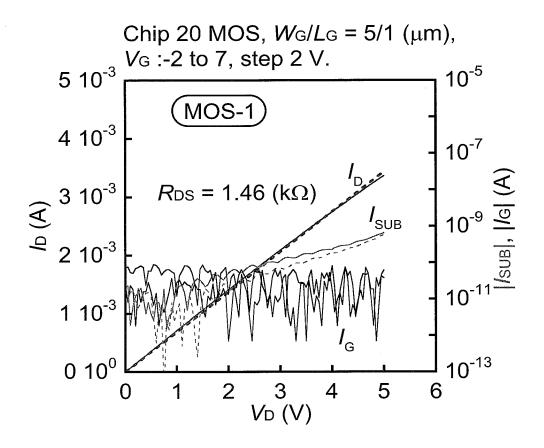

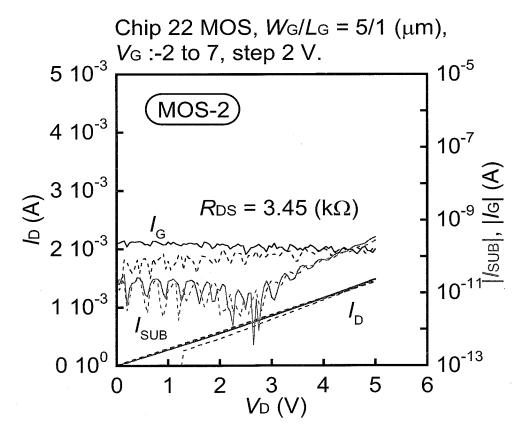

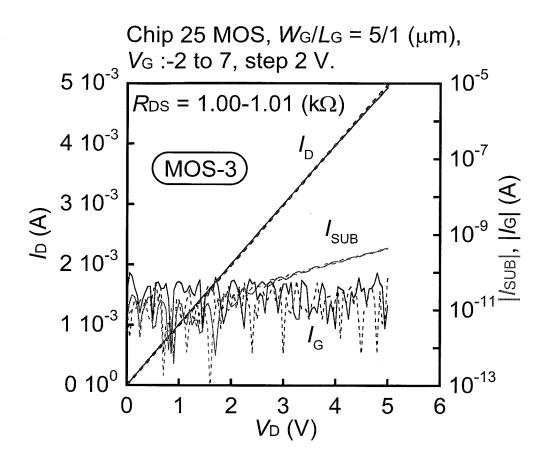

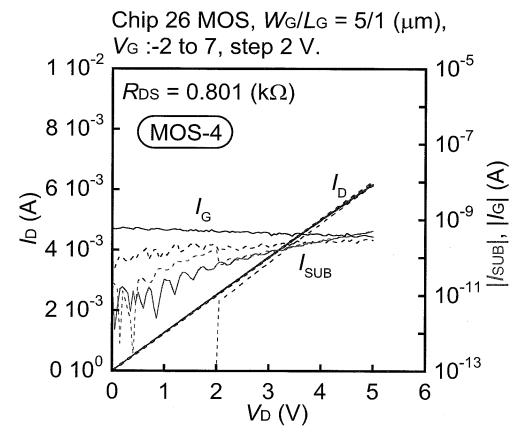

ゲート絶縁破壊後の MGS および MOS トランジスタの特性を図 5.4 と図 5.5 に示す。

図 5.4 (a) MGS トランジスタのゲート絶縁破壊後の特性 (デバイス #1&#2)

図 5.4 (b) MGS トランジスタのゲート絶縁破壊後の特性(デバイス #3&#4)

図 5.5 (a) MOS トランジスタのゲート絶縁破壊後の特性 (デバイス #1&#2)

図 5.5 (b) MOS トランジスタのゲート絶縁破壊後の特性 (デバイス #3&#4)

ゲート絶縁強制破壊後のMGSトランジスタの特性を図5.4に示す。ドレイン電流がゲート電圧にかかわらずドレイン電圧に直線的に依存して増加している。いいかえればほぼ純粋な抵抗が形成されていることがわかる。その抵抗の値は、のように求められた。

表 5.1 ゲート絶縁強制破壊後のトランジスタのソスードレイン間抵抗の値

| チップ番号        | MGS                     | MOS                     |

|--------------|-------------------------|-------------------------|

| デバイス #1 - 20 | $1.05~\mathrm{k}\Omega$ | 1.46 kΩ                 |

| デバイス #2 - 22 | $2.88~\mathrm{k}\Omega$ | $3.45~\mathrm{k}\Omega$ |

| デバイス #3 - 25 | $1.31~\mathrm{k}\Omega$ | $1.00~\mathrm{k}\Omega$ |

| デバイス #4 - 26 | $0.82~\mathrm{k}\Omega$ | $0.80~\mathrm{k}\Omega$ |

### 5.4 トランジスタの不揮発性メモリ効果

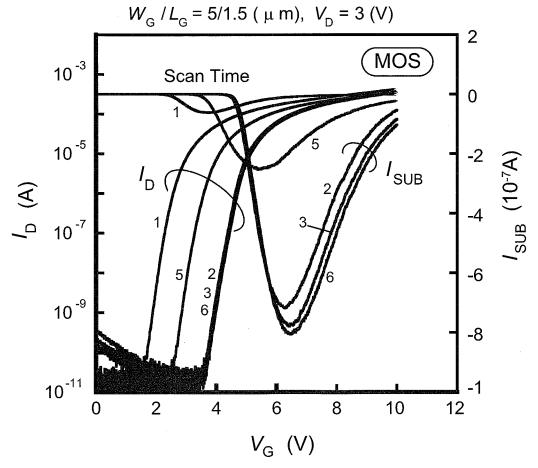

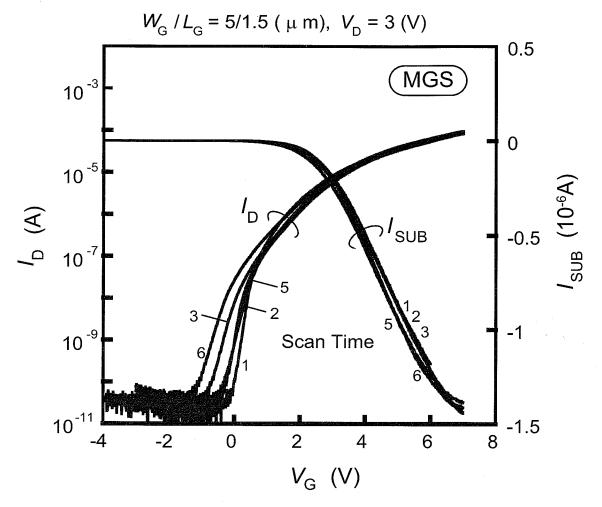

MGS および MOS トランジスタの  $I_D$ - $V_D$  特性や  $I_D$ - $V_G$  特性測定において、測定を繰り返特性が変化することが見いだされた。図 5.6 に MOS トランジスタの特性を、図 5.7 に MGS トランジスタの特性の変化を示す。

Chip 03 MOS

図 5.6 MOS トランジスタの特性のゲート電圧印加回数による特性変化 1-3 回目まで連続測定、4 回目: $V_{\rm G}$ =0  $\rightarrow$  -5 V、5-6 回目: 1-3 回目と同条件で連続測定。

# Chip 03 MGS

図 5.7 MGS ランジスタの特性のゲート電圧印加回数による特性変化 1-3 回目まで連続測定、4 回目: $V_{\rm G}$ =0  $\rightarrow$  -7V、5-6 回目: 1-3 回目と同条件で連続測定。

## 第6章 実験結果の考察

本章では、実験で見いだされた解析を要する現象を考察する。

## 6.1 MGS トランジスタのゲート耐圧破壊後の特性

図5.2 および5.3 に示したように、MGSトランジスタと MOSトランジスタのゲート絶縁強制破壊後のゲートリーク電流には明らかな差があり、MGSトランジスタの第2回目のリーク電流は絶縁破壊を起こしていないような状態である。おそらく、リーク電流経路が絶縁破壊を起こした大電流によって消滅し、結果として低いリーク電流が実現したものと思われる。この点で、MGSトランジスタには、何らかの放射線障害などに対する耐性が高いといえようか。

しかし、強制破壊後のトランジスタ特性は、図 5.4 および図 5.5 に示すように、MGSトランジスタおよび MOSトランジスタともソースとドレイン間には純抵抗が形成された特性を示している。

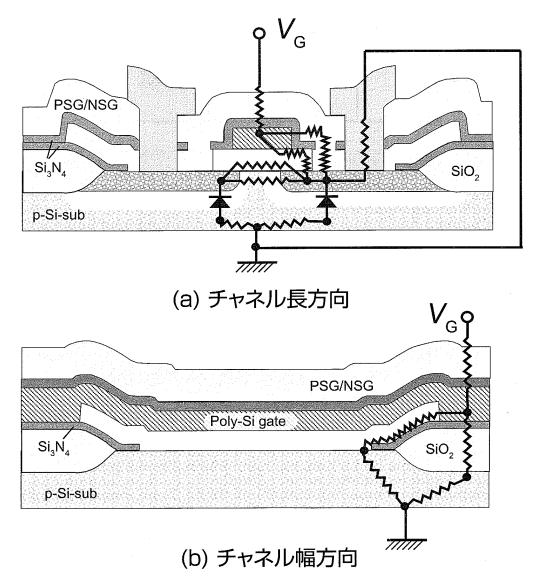

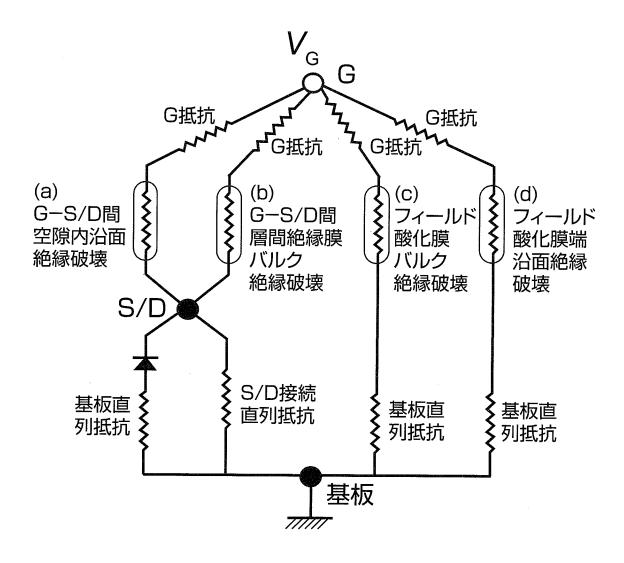

図 6.2 想定絶縁破壊経路の等価回路

そこで、どの部分が破壊したのかを考察してみよう。図 6.1 に想定できる電流経路を示し、図 6.2 にその等価回路を示した。

破壊する部分は、図6.2に示したように次に4カ所である。

- (a) ゲート-ソース / ドレイン間空隙内沿面絶縁破壊

- (b) ゲート-ソース / ドレイン間層間絶縁膜バルク絶縁破壊

- (c) フィールド酸化膜バルク絶縁破壊

- (d) フィールド酸化膜端沿面絶縁破壊

MGS トランジスタは絶縁破壊後、ゲートは高い耐圧を示しているので、(b)、(c)、および (d) は破壊していないと考えられる。それに比べると MOS トランジスタはよく知られた絶縁破壊後のリーク電流特性を示しており、50nm 厚の薄いゲート絶縁膜が破壊していると考えられる。

しかし、絶縁破壊後のソース - ドレイン間の純抵抗に近い抵抗の発生は何に起因するのであろうか。表 5.1 に示した、純抵抗の値は MGS と MOS では強い相関が見られる。この相関は測定デバイスのウェハ内の位置に依存しているように見える。

図 6.3 測定チップの位置

図 6.4 測定チップの位置

図 6.3 にウェハ内のチップの位置、図 6.4 ににその等価回路を示した。同じチップ内の MGS と MOS トランジスタは隣接しており、最も近い位置にある。ウェハ内の何らかの 分布がトランジスタのソース – ドレイン間の抵抗に影響しているのがわかる。それが何であるか今後の解析が必要である。

### 6.2 トランジスタの不揮発性メモリ効果

本研究で試作したトランジスタは、ゲートダミー膜をバッファ HF 溶液で除去する際に 余分に除去されるのを抑制するために、チャネル幅方向のフィールド酸化膜の端を  $Si_3N_4/SiO_2$  二重膜で保護している。この部分は MNOS(metal-nitride-oxide-semiconductor) 型の 不揮発性メモリである。つまり、図 6.5 に示すように、中央部分の通常の MOS トランジスタと端の不揮発性メモリ MNOS 型トランジスタが並列に接続されていることになる。

このように考えれば、図 5.5 と図 5.6 の特性は説明できる。MGS では比誘電率が 1 で SiO2 の 1/4 の低い誘電率の気体が挿入されているので、 $Si_3N_4/SiO_2$  二重膜に十分な電界が印加されず、しきい電圧の変異は少ないと考えられる。

図 6.5 MGS および MOS トランジスタの等価ゲート構造

## 第7章 結論

## 7.1 研究結果のまとめ

通常の MOSFET (metal-oxide-semiconductor field-effect transistor:金属-酸化膜-半導体 電界効果トランジスタ)の酸化膜部分を気体に置き換えた MGSFET (metal-gassemiconductor field-effect transistor:金属-気体-半導体 電界効果トランジスタ)を 提案し、試作・評価した。この MGSFET はごく薄いゲート絶縁膜が存在しないことにより、 放射線障耐性やホットキャリヤ耐性が高いことを実現することを目指している。試作・評価により下記の結果が得られた。

- (1) MGS トランジスタの相互コンダクタンスは MOS の約 1/4 で、これは気体の誘電率が、酸化膜(SiO<sub>2</sub>)のほぼ 1/4 であることで説明できる。

- (2) MGSトランジスタおよび MOSトランジスタともにゲート電圧の印加回数が増す としきい電圧が変位する。トランジスタ構造の一部に MNOS (metal-nitride-oxidesemiconductor) 型の不揮発性メモリが形成されていることで説明できる。

- (3) ゲート電極に高電圧を印加しゲート絶縁を破壊した後、MOSトランジスタには恒常的 にゲートから基板にリーク電流経路が形成されるのに対し、MGSトランジスタはむし ろリーク電流経路が消失して耐圧が向上する。

- (4) ただ、ゲート絶縁を破壊した後には、MGSトランジスタおよび MOSトランジスタの ソースードレイン間には純抵抗が形成され、トランジスタ動作は行わなくなる。

#### 7.2 今後に残された課題

MGS および MOS トランジスタを試作・評価した結果、下記の課題が明らかとなった。 今後、解決しなければならない課題である。

- (1) 不揮発性メモリ型の特性により、放射線障耐性やホットキャリヤ耐性の測定ができなかった。フィールド酸化膜端の酸化膜を保護するために被着した  $Si_3N_4$  膜によるものと推定されるので、 $Si_3N_4$  膜を用いない構造を見いだす必要がある。

- (2) 強制的にゲート絶縁を破壊する現在のランプ電圧印加法はトランジスタそのものを破壊するので別の測定法を適用する必要がある。

#### 謝辞

本研究は、広島大学ナノデバイス・システム研究センターで行われたものであり、センター の運営に貢献されている多くの方々に深く感謝致します。