## Reliable extraction of the energy distribution of Si/SiO<sub>2</sub> interface traps in ultrathin metal–oxide–semiconductor structures

Quazi Deen Mohd Khosru,<sup>a)</sup> Anri Nakajima,<sup>b)</sup> Takashi Yoshimoto, and Shin Yokoyama Research Center for Nanodevices and Systems, Hiroshima University, 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan

(Received 18 February 2002; accepted for publication 27 March 2002)

A simple and effective method for the extraction of interface trap distribution in ultrathin metal– oxide–semiconductor (MOS) structures is presented. By a critical analysis of bipolar-pulse-induced currents through MOS capacitors, a technique is developed to determine the energy distribution of the interface traps without requiring the knowledge of surface potential and doping profile in the semiconductor. The proposed technique can be efficiently used to probe electrical stress, hot-carrier, and radiation-induced interfacial degradations in ultrathin MOS structures. © 2002 American Institute of Physics. [DOI: 10.1063/1.1481194]

The generation of interface traps at the semiconductor/ oxide interface of metal-oxide-semiconductor (MOS) structures has long been demonstrated as one of the prime factors behind the degradation of MOS device characteristics. Characterization of the interface traps thus simultaneously has been an important job for accurate estimation of device lifetime and reliability. Several techniques have been proposed for the determination of the density of these traps and their energy distribution in the forbidden energy gap of the semiconductor materials.<sup>1-5</sup> Capacitance–voltage  $(C-V)^{4-6}$  and charge pumping techniques<sup>7,8</sup> are widely employed for the characterization of the interface traps in large-area MOS capacitors and small-area transistors, respectively. Although the charge pumping technique is an efficient approach to the determination of the interface traps in small-area transistors, it cannot be effectively applied on large-area capacitors. On the other hand, the accuracy of estimated interface trap density using the C-V technique is dependent on the accuracy of capacitance measurements. Terman<sup>3</sup> showed that interface trap capacitance could be determined from frequency dispersion of MOS capacitance. This is essentially a difficult and indirect method as the interface trap capacitance is extracted from a measured capacitance that consists of oxide capacitance, depletion capacitance, and the interface trap capacitance. A modified method to determine interface trap distribution from a measured conductance was proposed for its direct relationship with the interface traps.<sup>1</sup> Again, this method is not quite convincing as the value of the required conductance  $G_p$  is extracted from the maximum value of  $G_p/\omega$  as a function of  $\omega\tau$ , where  $\omega$  is the angular frequency and  $\tau$  is interface trap lifetime. Berglund<sup>4</sup> described a method for determining the energy distribution of interface traps by using low-frequency capacitance measurements on MOS structures, while Koukab et al.<sup>6</sup> demonstrated a highfrequency C-V method for the analysis of interface traps. However, various approximations and assumptions are usually made for the study of interface properties using the C-V measurements, which are not always well justified. For instance, both the low- and high-frequency capacitance methods use a theoretical curve of semiconductor capacitance as a function of surface potential, which itself is dependent on approximated doping profile and other assumed parameters. Moreover, accurate measurements of C-V characteristics are very difficult in MOS structures with ultrathin oxides due to large intrinsic tunneling leakage. So, the standard C-V method cannot be applied for reliable extraction of the interface trap distribution in ultrathin oxides and hence cannot be used to investigate stress induced interfacial damages as well. Nevertheless, these methods have long been used to characterize interface traps despite low quantitative reliability. Therefore, an easy and more reliable method is highly desired for accurate characterization of interface traps in ultrathin oxide MOS capacitors. In this letter, we present a simple and reliable method for extracting the energy distribution of interface traps using bipolar pulse induced current measurements directly on the MOS capacitors.

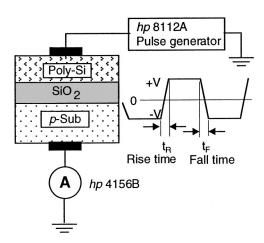

Conventional MOS capacitors with SiO<sub>2</sub> dielectrics are used in this study. The capacitors are fabricated using *p*-type Si (001) wafers (~10  $\Omega$  cm). Gate oxide (~3.0 nm) is grown at 850 °C in dry oxygen ambient. After the growth of the gate SiO<sub>2</sub>, a 200 nm thick polycrystalline silicon (poly-Si) gate is formed using POCl<sub>3</sub> diffusion at 900 °C for doping and activation annealing. The capacitors thus fabricated are subjected to bipolar-voltage-pulse-induced current measurements with a view to extract energy distribution of interface traps at the Si/SiO<sub>2</sub> interface.

An experimental setup is illustrated in Fig. 1. A bipolar pulse train of fixed amplitude and frequency ( $\pm 3$  V, 10 kHz) is applied to the gate of the MOS capacitor from a pulse generator (*HP* 8112A). The pulse fall/rise time ( $t_F/t_R$ ) is gradually varied (keeping the rise/fall time constant) and the corresponding change in substrate current is monitored using a semiconductor parameter analyzer (*HP* 4156B). All experimental measurements are automated using a desktop personal computer. Under the proposed measurement conditions, the MOS device is switched between inversion and accumulation by the bipolar gate pulse. Electrons fill the

3952

Downloaded 17 Jun 2007 to 133.41.149.126. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>On leave from Bangladesh University of Engineering and Technology, Dhaka, Bangladesh.

<sup>&</sup>lt;sup>b)</sup>Author to whom correspondence should be addressed; electronic mail: nakajima@sxsys.hiroshima-u.ac.jp

<sup>© 2002</sup> American Institute of Physics

FIG. 1. Schematic illustration of experimental setup for measuring bipolar pulse induced current in MOS capacitors. Pulse fall/rise time is gradually changed during measurements in order to scan the energy levels of interface traps in the upper/lower half of the band gap.

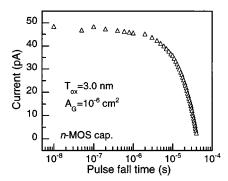

traps at the Si/SiO<sub>2</sub> interface during inversion. Oxide traps existing within a few angstroms from the Si/SiO<sub>2</sub> interface may also be filled due to a tunneling mechanism.<sup>7,9</sup> As the gate bias is reversed, bringing the device into accumulation through depletion, some of the traps lose electrons by emission. Only those traps holding the captured electrons until the device is moved into complete accumulation may give rise to a net flow of charge into the substrate through a recombination with the accumulated majority carriers. This is the so-called charge pumping effect. In the case of MOS transistors, the substrate current thus measured is known as charge pumping current and is reliably used for characterizing the Si/SiO<sub>2</sub> interface traps. However, in the case of MOS capacitors, the measured substrate current is not exactly the charge pumping current, rather it is a net tunneling current through the capacitor. Therefore, unlike MOS transistors, the interface trap density cannot be estimated directly from the measured substrate current. Here, we introduce the concept of using bipolar pulse induced currents for probing interface traps in MOS capacitors. Figure 2 exhibits the substrate current as a function of the pulse fall time measured using the experimental setup shown in Fig. 1. Only the trapped interface electrons that can follow the change in pulse fall time can bring about a change in the measured current. Hence, the difference between two values measured under two different pulse fall times is essentially caused by the interface traps, which are responding to the change of emission time constant due to a change in the pulse fall time. Thus the interface

trap charge probed between two measurements can be obtained as

$$Q_{\rm it} = (I_{S0} - I_S)(t_F - t_{F0}), \tag{1}$$

where  $I_{S0}$  is the measured current corresponding to the minimum pulse fall time,  $t_{F0}$  is permitted by the pulse generator, and  $I_S$  is the measured current for any fall time  $t_F$ . In fact, the application of a bipolar pulse with variable fall time scans the trap levels in the upper half of the band gap (acceptor-like traps) when the surface is changed from inversion to accumulation.<sup>7,8</sup> So, the trapped charges that are being probed between two measurements can also be expressed as

$$Q_{\rm it} = qA_G \int D_{\rm it}(E)dE, \qquad (2)$$

where *q* is the electronic charge,  $A_G$  is the gate area, and  $D_{it}(E)$  is the interface trap density at an energy *E*. The limits of integration in Eq. (2) should be selected as the energies corresponding to the pulse fall times. From the simple theory of emission,<sup>7,10</sup> an expression for the energy *E* can be obtained as

$$E - E_c = kT \ln \left[ \nu_{\rm th} \sigma_n n_i \frac{|V_{\rm IA}|}{|V_{\rm PH}|} t_F \right], \tag{3}$$

where  $E_c$ ,  $v_{\text{th}}$ ,  $\sigma_n$ , and  $n_i$ , are the silicon conduction band energy, thermal velocity, electron capture cross section, and intrinsic carrier density, respectively.  $V_{\text{IA}}$  is the pulse voltage drop from inversion to the onset of accumulation and  $V_{\text{PH}}$  is the pulse height. It is obvious in Eq. (3) that the interface traps at different energies can be probed by varying the pulse fall time  $t_F$ . Now, the derivative of  $Q_{\text{it}}$  with respect to pulse fall time  $t_F$  is given by

$$\frac{dQ_{\rm it}}{dt_F} = qA_G D_{\rm it}(E) \frac{dE}{dt_F},\tag{4}$$

and using the above equations, an expression for the interface traps in the upper half of the band gap can be obtained as

$$D_{\rm it}(E) = \frac{t_F}{qA_GkT} \frac{dQ_{\rm it}}{dt_F}.$$

(5)

Likewise, the energy distribution of the interface traps in the lower half of the band gap can be obtained by deriving a similar set of equations and measuring the pulse rise time dependence of the capacitor currents.

Energy distribution of interface traps thus obtained using the proposed method is presented in Fig. 3 (solid lines). A standard value of  $6.6 \times 10^{-15}$  cm<sup>2</sup> for electron and hole capture cross section<sup>9</sup> has been used to calculate the energy distribution. The triangles in Fig. 3 represent the interface traps obtained by using the conductance method<sup>1</sup> on the same samples, while the circles represent the interface traps estimated from the charge pumping currents measured on *n*-MOS transistors fabricated with identical oxide thickness (2.8 nm) and process flow. These results demonstrate that the proposed method has estimated the interface trap distribution in the forbidden energy gap of silicon. Note that the increasing feature of the interface trap density toward the band's

FIG. 2. Measured current as a function of pulse fall time. edges and the magnitudes are in good agreement with the Downloaded 17 Jun 2007 to 133.41.149.126. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

FIG. 3. Energy distribution of interface trap density as obtained using the proposed method. Triangles represent the interface traps obtained by the conductance method using the same n-MOS capacitors, while circles represent the interface traps obtained by the charge pumping method using n-MOS transistors with identical oxide thickness (2.8 nm).

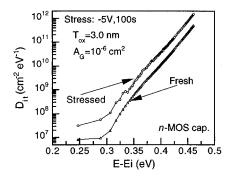

reports of energy distribution of interface traps in MOS structures.<sup>1,7,9</sup> The validity and reliability of the proposed method is further examined by evaluating electrical stress induced interface trap generation. The interface trap densities measured before and after a constant voltage stressing at -5 V for 100 s are presented in Fig. 4. It reveals that the interfacial damage caused by high voltage stressing has been well measured. The nonsaturating feature of the distribution, as it approaches the band's edges (Figs. 3 and 4) can be explained as the result of carrier emission from bulk traps existing near the interface.

In summary, a simple and effective method of obtaining trap distribution at the  $Si/SiO_2$  interface of MOS structures has been demonstrated. Bipolar pulse induced current through MOS capacitors and its dependence on the pulse fall/rise time is exploited to characterize the interface traps. The developed method does not require the knowledge of surface potential and doping profile curves and is free from

FIG. 4. Interface trap distribution in fresh and stressed (@-5 V for 100 s) samples.

any approximations and assumptions that are usually made in C-V methods. Further, the method has been used to evaluate electrical stress induced interface trap generation in ultrathin MOS structures and hence can as well be used to probe hot-carrier and radiation induced interfacial damages. It is worth mentioning that the proposed method is a more accurate and reliable tool for quantitative characterization of the interface traps than the capacitance or the conductance methods that are often considered as qualitative.

- <sup>1</sup>E. H. Nicollian and A. Goetzberger, Appl. Phys. Lett. 7, 216 (1965).

- <sup>2</sup>P. V. Grey and D. M. Brown, Appl. Phys. Lett. 8, 31 (1966).

- <sup>3</sup>L. M. Terman, Solid-State Electron. 5, 285 (1962).

- <sup>4</sup>C. N. Berglund, IEEE Trans. Electron Devices 13, 701 (1966).

- <sup>5</sup>M. Kuhn, Solid-State Electron. **13**, 873 (1970).

- <sup>6</sup>A. Koukab, A. Bath, and E. Losson, Solid-State Electron. **41**, 635 (1997).

- <sup>7</sup>G. Groeseneken, H. E. Maes, N. Beltran, and R. F. DeKeersmaecker, IEEE Trans. Electron Devices **31**, 42 (1984).

- <sup>8</sup>M. Koyanagi, Y. Baba, K. Hata, I. W. Wei, A. G. Lewis, M. Fuse, and R. Bruce, IEEE Electron Device Lett. **13**, 152 (1992).

- <sup>9</sup>M. Giannini, A. Pacelli, A. L. Lacaita, and L. M. Perron, IEEE Electron Device Lett. **21**, 405 (2000).

- <sup>10</sup>S. M. Sze, *Physics of Semiconductor Devices* (Wiley, New York, 1981).